引言:本文我们介绍下Intel FPGA板级设计相关的内容,主要对板级设计一些需要考虑的关键内容进行描述。

1.概述

许多系统设计中,一个典型的设计流程开始于市场需求文档(MRD),该文档说明了高水平的可行性报告和将要开发产品的技术要求。在该文档批准后,项目负责团队会利用它产生一个更加详细的产品需求文档(PRD)。产品需求文档典型的说明产品架构的实现,甚至明确某些产品中要求的关键器件。设计者会根据产品需求文档产生详细的设计说明书。

在复杂的系统设计中,由于FPGA可编程的特性和集成了高速收发器,使得它是一个频繁使用的关键器件。由于它的灵活性,FPGA已经成为系统设计的核心器件,允许设计者容易的桥接不同的技术和驱动高速背板。然而,正是因为它的灵活性,如果FPGA设计者不熟悉FPGA设计过程,使得FPGA设计可能成为一种挑战。

2.FPGA设计流程

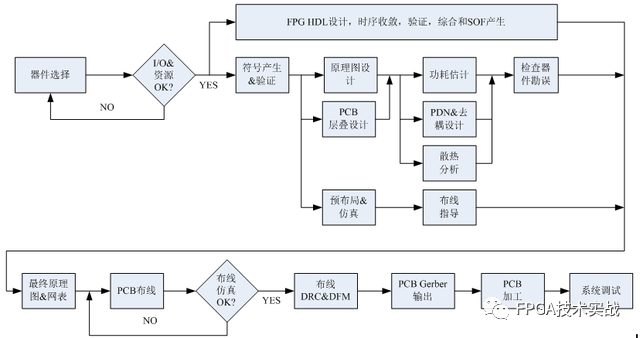

图1显示了典型的Intel FPGA设计流程。

图1、典型的Intel FPGA设计流程

2.1 器件选择

典型的FPGA设计开始于选择最能满足系统需求的Altera器件开始,如I/O管脚数量、LVDS通道数、时钟和PLL资源、嵌入式RAM数量、DSP模块以及收发器个数等等。当一个选择的器件的资源和性能能够满足需求,原理图和FPGA HDL设计可以进行了。

2.2 原理图符号产生

原理图开始设计首先要设计FPGA符号。由于FPGA 大部分I/O管脚的可编程性,在此阶段小心的管脚规划可以帮助减少布线的复杂度和减少PCB层数。利用一下惯例产生原理图符号。

考虑电路板上系统级的器件互联布局规划,尽可能减少布线阶段的信号交叉。可编程I/O命名时最好可以指示它们暗含的功能,以使原理图具有可读性。

命名专用管脚,如配置管脚和电源管脚,可以使用它们的专用功能命名。

在QuartusII软件中编译最终的管脚分配,以确保满足器件要求和I/O布局规则。

2.3 原理图设计

当一个已验证的符号完成后,根据它们的使用要求,原理图输入连接所有的FPGA管脚到它们各自的接口。Intel FPGA管脚可以分成以下几种类型:

配置和JTAG管脚。由于FPGA是基于SRAM工艺的器件,因此每次器件上电时,它们都要求配置数据重新加载。这些管脚利用QuartusII软件产生的配置数据编程FPGA。有些管脚是专用的配置管脚,而其他管脚也可以在器件配置完成后用作用户I/O来使用。Altera器件支持多种配置方案,具体选择根据设计需求。时钟和PLL输入。FPGA内部的时钟将其分为几个区域。例如,Stratix IV器件,时钟区域被分为全局时钟网络、局部时钟网络和PLL输出。专用的时钟输入管脚提供外部时钟源输入到这些全局时钟网络和局部时钟网络,以及器件内的PLL输入。由于专用时钟输入管脚和PLL的固定位置,并不是每个时钟管脚都可驱动器件所有的区域和PLL资源。因此时钟管脚分配时必须考虑该管脚可用的内部时钟域和PLL资源。 用户I/O。I/O管脚被设计成支持宽范围的工业I/O标准,允许灵活地满足不同技术需求。I/O管脚分配在器件的成为I/O BANK的区域。基于器件,这些I/O管脚可以提供附加的特性,如片上终端电阻、可编程驱动电流、可编程沿速率和为改善信号完整性的可编程延迟,不需要外部器件控制。然而,由于在一个I/O BANK内只能提供一个I/O电压和参考电压,使用不同VCCIO货参考电VREF的混合I/O标准在同一个BANK内是不允许的。因此,要仔细进行管脚规划,以尽可能提高BANK管脚的利用率。使用一下选项检查I/O管脚分配。

为每一个I/O选择一个稳定的信号类型和I/O标准确保目标I/O BANK中支持恰当的I/O标准同一个BANK内的I/O管脚分享同一个VCCIO电压验证每个I/O BANK内所有的输出信号电平满足VCCIO电压验证每个I/O BANK内所有的参考电压使用I/O BANK参考电压VREF检查I/O支持的LVDS特性为存储器接口使用专用的DQ/DQS管脚和DQ信号组QuartusII软件中验证过的管脚分配

2.4 高速收发器

高速收发器管脚实现如PCIe、SATA、10G以太网、XAUI等等。成功的串行接口设计的前提是,很好的理解高速设计技术以最小I/O抖动和最大收发器张开的眼图。

2.5 电源供电

电源管脚为数字和模拟模块提供电源,如逻辑核资源、I/O、PLL及收发器。模拟PLL和收发器的电源轨对噪声是非常敏感的,因此要仔细设计隔离和去耦,以最小化噪声对性能的影响。电源轨的隔离可以在PCB层叠和板级布线时定义。

2.6 PCB层叠设计

PCB层叠设计与原理图输入是同时进行的,PCB层叠设计要与PCB制造商紧密沟通。大部分PCB制造商免费提供详细的层叠设计,以满足工程要求。一个典型的PCB层叠通常包含PCB使用的材料、层数、层的顺序、阻抗控制要求、PCB填充以及成品厚度等。早期的PCB层叠完成对于执行布线前仿真以及对PCB布线师制定布线规则是非常有用的。

2.7 电源设计和去耦

FPGA设计一个挑战的部分是实现电源分配和去耦网络。利用Intel的早期功耗估计器可以进行功耗估计,或参考旧设计进行资源功耗估算。利用电源分配网络工具可以决定去耦需求。

2.8 散热管理

除了利用EPE估计功耗外,还可以估算结温。利用EPE工具,你可以确定散热方案,以使FPGA工作在安全的操作范围内。

2.9 布线前仿真

为了验证关键信号的布线的信号完整性,Altera提供了完整的IBIS和HSPICE I/O缓冲模型,允许系统设计者进行信号完整性仿真。这对决定关键网络端接要求、串扰影响、长度约束和其布线规则是非常有用过的。

2.10 布线设计

布线设计是将原理图设计转换成板级物理表征。一个普通的原则是提供布线者一个详细的文档,该文档说明了板级布线所有的物理要求。通常包含详细的电路板尺寸、层叠信息和顺序、满足信号完整性的所有的设计规则和其他规则满足电路板制造商的要求。当布线者理解这些布线要求后,就可以开始进行布线设计。

2.11 布线后仿真

当关键的布线完成后,Altera推荐进行布线后仿真。当布线后仿真确认关键信号完成性完好时,布线者可以最终完成全部布线工作,以及后续工作。

侯明娟:骁龙新技术+生成式AI创新赋能顶级移动体验

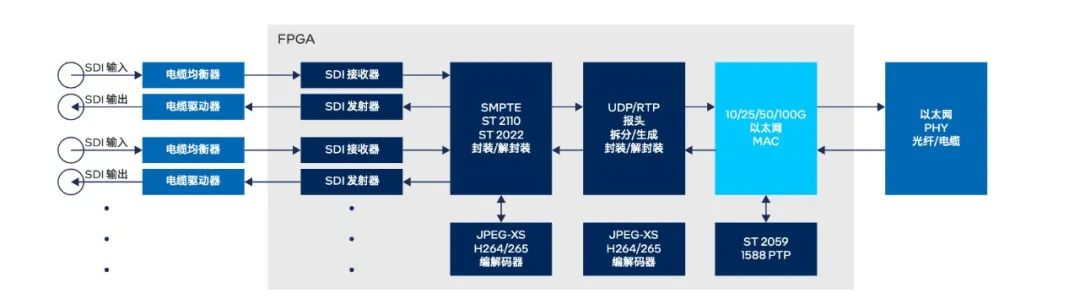

侯明娟:骁龙新技术+生成式AI创新赋能顶级移动体验 白皮书 | 面向实时视频制作工作流程的 FPGA

白皮书 | 面向实时视频制作工作流程的 FPGA 如何学习可编程逻辑控制器(PLC)?

如何学习可编程逻辑控制器(PLC)? 如何学习可编程控制器PLC?如何选择PLC?

如何学习可编程控制器PLC?如何选择PLC?

慧聪电子网微信公众号

慧聪电子网微信公众号

慧聪电子网微信视频号

慧聪电子网微信视频号

精彩评论