10月12日,新思科技(Synopsys, Inc.)宣布,Achronix 公司使用新思科技的综合设计、验证和IP解决方案,其新Speedster7t FPGA首次通过硅验证。高性能计算和机器学习系统的关键是高片外存储器带宽,为使Speedster7t FPGA支持高带宽和人工智能/机器学习(AI/ML)工作负载, Achronix选择使用新思科技的解决方案缩短其产品上市时间。

新思科技的DesignWare IP产品组合帮助Achronix完美的实现了Speedster7t FPGA所需的存储器性能和实时数据连接的需求。与市面上其他解决方案相比,DesignWare Logic Library IP可将占用面积降低4%,时序提升8%,对于高速设计而言,这两项指标的提升至关重要。此外,DesignWare Embedded Memory IP(包括双端口SRAM)可降低Speedster7t FPGA的功耗,DesignWare DRD4 IP具有全面和广泛的可靠性、可用性和可维护性(RAS)能力。PCI Express (PCIe) 5.0具有低延迟特性,可支持16条链路和512位数据路径宽度,因此可提供更大的带宽和更好的功耗效率。Achronix非常期待与新思科技的长期合作,并计划在其下一个设计中继续使用DesignWare IP。

在外形银子受面积和功率限制的情况下,新思科技的Fusion设计平台可帮助Achronix实现具有市场塑造力的高带宽计算所需的性能。测试、执行和金牌签核技术的独特融合使Achronix能够在系统性规模层面更大限度地减少设计余量,实现更好的整体设计收敛,并帮助Achronix加速实现首次硅成功。

新思科技的定制设计平台有助于减少在7纳米Speedster7t FPGA中设计、布局和模拟高性能定制电路所需的时间和精力,具有特定节点的特性,可提高开发者的工作效率。

Achronix还采用了新思科技Verification Continuum®平台中的关键功能验证产品来验证其FPGA。新思科技的VCS®仿真解决方案可以加速仿真性能,而其验证IP可提供更快的验证环境创建速度, VC SpyGlass RTL静态签核工具则提供了早期设计漏洞检测功能。

侯明娟:骁龙新技术+生成式AI创新赋能顶级移动体验

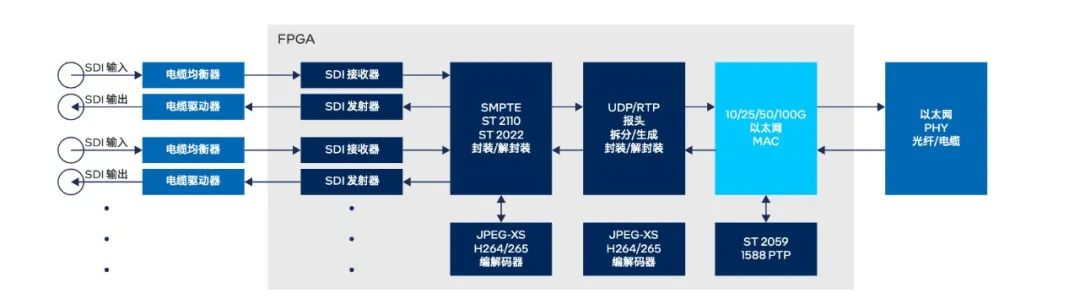

侯明娟:骁龙新技术+生成式AI创新赋能顶级移动体验 白皮书 | 面向实时视频制作工作流程的 FPGA

白皮书 | 面向实时视频制作工作流程的 FPGA 如何学习可编程逻辑控制器(PLC)?

如何学习可编程逻辑控制器(PLC)? 如何学习可编程控制器PLC?如何选择PLC?

如何学习可编程控制器PLC?如何选择PLC?

慧聪电子网微信公众号

慧聪电子网微信公众号

慧聪电子网微信视频号

慧聪电子网微信视频号

精彩评论