GPIO的功能,简单说就是可以根据自己的需要去配置为输入或输出。但是在配置GPIO管脚的时候,常会见到两种模式:开漏(open-drain,漏极开路)和推挽(push-pull)。

Push-Pull推挽输出

输出的器件是指输出脚内部集成有一对互补的MOSFET,当Q1导通、Q2截止时输出高电平;而当Q1截止导通、Q2导通时输出低电平。

Push-pull输出,实际上内部是用了两个晶体管(transistor),此处分别称为top transistor和bottom transistor。通过开关对应的晶体管,输出对应的电平。top transistor打开(bottom transistor关闭),输出为高电平;bottom transistor打开(top transistor关闭),输出低电平。Push-pull即能够漏电流(sink current),又可以集电流(source current)。其也许有,也许没有另外一个状态:高阻抗(high impedance)状态。除非Push-pull需要支持额外的高阻抗状态,否则不需要额外的上拉电阻。

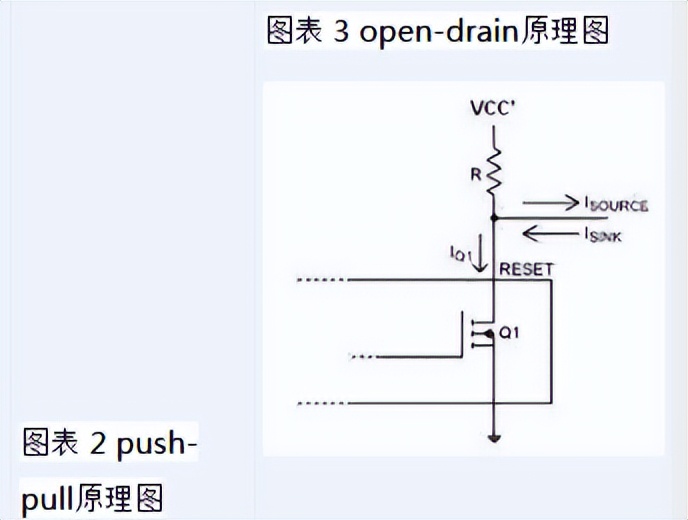

Open-Drain开漏输出

开漏电路就是指以MOSFET的漏极为输出的电路。指内部输出和地之间有个N沟道的MOSFET(Q1),这些器件可以用于电平转换的应用。输出电压由Vcc'决定。Vcc'可以大于输入高电平电压VCC(up-translate)也可以低于输入高电平电压VCC(down-translate)。

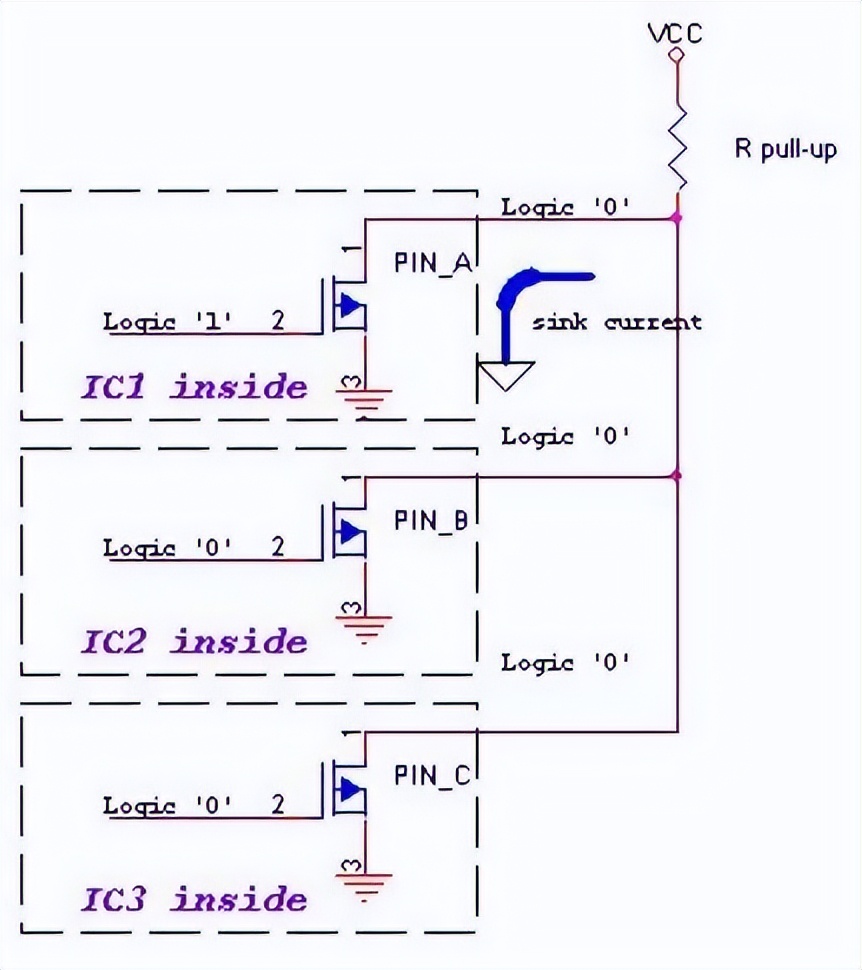

Open-drain输出,则是比push-pull少了个top transistor,只有那个bottom transistor。(就像push-pull中的那样)当bottom transistor关闭,则输出为高电平。此处没法输出高电平,想要输出高电平,必须外部再接一个上拉电阻(pull-up resistor)。Open-drain只能够漏电流(sink current),如果想要集电流(source current),则需要加一个上拉电阻。

老外的理解

图表 4 open-drain“线与”功能

优点

Push-Pull推挽输出

(1)可以吸电流,也可以贯电流;

(2)和开漏输出相比,push-pull的高低电平由IC的电源低定,不能简单的做逻辑操作等。

Open-Drain开漏输出

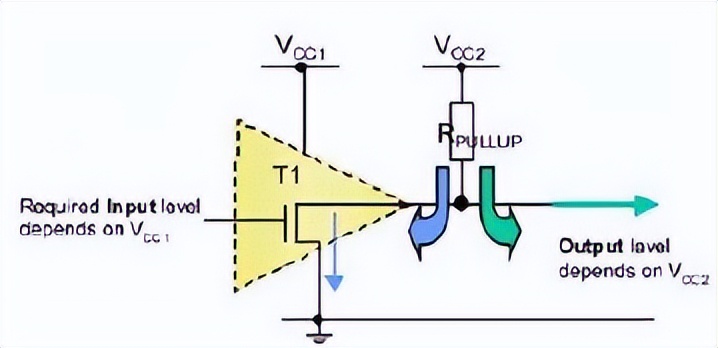

(1)对于各种电压节点间的电平转换非常有用,可以用于各种电压节点的Up-translate和down-translate转换

(2)可以将多个开漏输出的Pin脚,连接到一条线上,形成“与逻辑”关系,即“线与”功能,任意一个变低后,开漏线上的逻辑就为0了。这也是I2C,SMBus等总线判断总线占用状态的原理。

(3)利用 外部电路的驱动能力,减少IC内部的驱动。当IC内部MOSFET导通时,驱动电流是从外部的VCC流经R pull-up ,MOSFET到GND。IC内部仅需很下的栅极驱动电流。

(4)可以利用改变上拉电源的电压,改变传输电平:图表 5 open-drain输出电平的原理,IC的逻辑电平由电源Vcc1决定,而输出高电平则由Vcc2决定。这样我们就可以用低电平逻辑控制输出高电平逻辑了。

缺点

Push-Pull推挽输出

一条总线上只能有一个push-pull输出的器件;

在CMOS电路里面应该叫CMOS输出更合适,因为在CMOS里面的push-pull输出能力不可能做得双极那么大。输出能力看IC内部输出极N管P管的面积。push-pull是现在CMOS电路里面用得最多的输出级设计方式

Open-Drain开漏输出

开漏Pin不连接外部的上拉电阻,则只能输出低电平。当输出电平为低时,N沟道三极管是导通的,这样在Vcc'和GND之间有一个持续的电流流过上拉电阻R和三极管Q1。这会影响整个系统的功耗。采用较大值的上拉电阻可以减小电流。但是,但是大的阻值会使输出信号的上升时间变慢。即上拉电阻R pull-up的阻值 决定了逻辑电平转换的沿的速度。阻值越大,速度越低功耗越小。反之亦然。

塔克热系统在中国光博会隆重推出高性能光电应用中的最新主动制冷技术

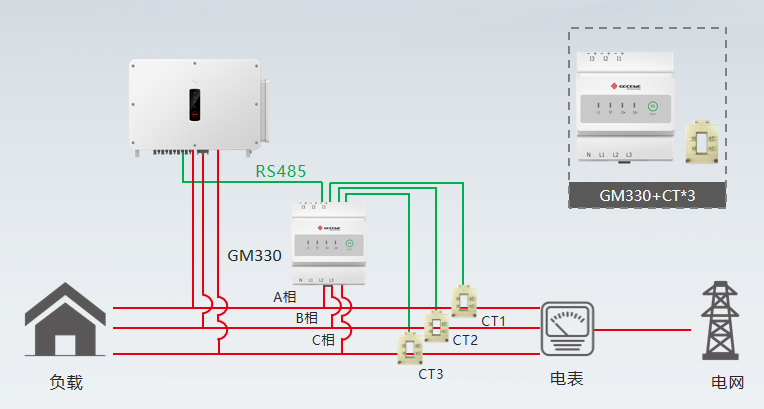

塔克热系统在中国光博会隆重推出高性能光电应用中的最新主动制冷技术 固德威防逆流安装调试指南

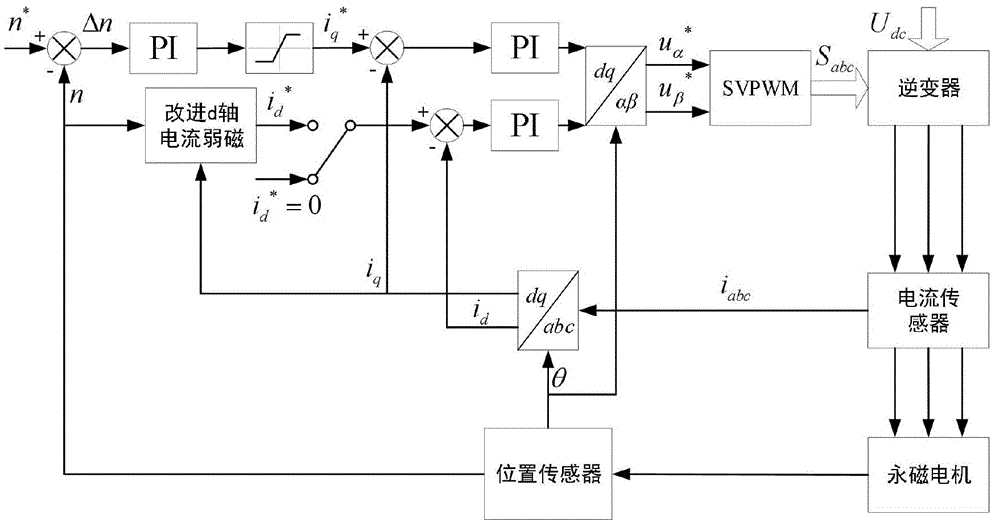

固德威防逆流安装调试指南 无刷电机弱磁控制:技术原理与实战应用

无刷电机弱磁控制:技术原理与实战应用 用于离线式开关电源的内部电源电路

用于离线式开关电源的内部电源电路

慧聪电子网微信公众号

慧聪电子网微信公众号

慧聪电子网微信视频号

慧聪电子网微信视频号

精彩评论