近日,美国麻省理工学院(MIT)和芝加哥大学的研究人员开发了一种新技术,可以让芯片按照预定的设计和结构自行组装。

这项技术有望进一步推进有着50年历史的“摩尔定律”,从而继续压缩计算设备的成本。该研究项目的重点是在芯片上自行组装线路,而这恰恰是芯片制造行业最大的挑战之一。

有了这种技术,就不必像现有的方式那样在硅片上蚀刻细微特征,而是可以利用名为嵌段共聚物(block copolymer)的材料进行扩张,并自行组装成预定的设计和结构。

MIT化学工程系教授卡伦·格里森(Karen Gleason)表示,这种自组装技术需要向现有的芯片生产技术中增加一个步骤。

现在的生产技术要利用长波光在硅晶圆上烧制出电路形态。目前的芯片需要采用10纳米工艺,但很难使用同样的波长填满更小的晶体管。EUV光刻技术有望降低波长,在芯片上蚀刻出更细微的特征。这种技术有望实现7纳米工艺,但即便已经投资了数十亿美元研发资金,这种技术依然很难部署。

MIT认为,他们的新技术很容易融入现有生产技术,无需增加太多复杂性。该技术可以应用于7纳米生产工艺,有关这项技术的论文已于本周发表在《Nature Nanotechnology》期刊上。

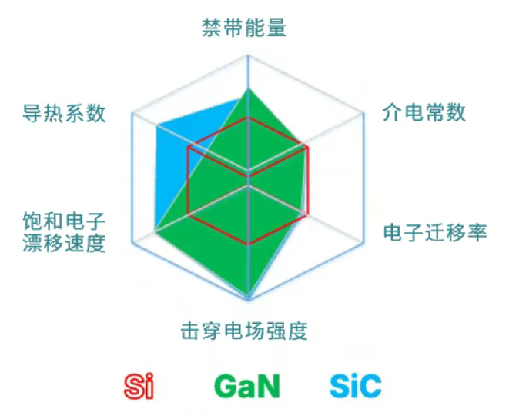

碳化硅赋能浪潮教程:SiC JFET驱动工业与服务器电源革新

碳化硅赋能浪潮教程:SiC JFET驱动工业与服务器电源革新 【首发】上海晶珩发布树莓派CM5龙虾盒子!要知道,你离AI私有化只差一个盒子!

【首发】上海晶珩发布树莓派CM5龙虾盒子!要知道,你离AI私有化只差一个盒子! 腾讯云TVP走进银河通用×NVIDIA×福田戴姆勒,解码AI驱动产业硬核突围之路

腾讯云TVP走进银河通用×NVIDIA×福田戴姆勒,解码AI驱动产业硬核突围之路 OpenClaw + 树莓派全栈部署手册:上海晶珩整理的最全避坑指南!

OpenClaw + 树莓派全栈部署手册:上海晶珩整理的最全避坑指南!

慧聪电子网微信公众号

慧聪电子网微信公众号

慧聪电子网微信视频号

慧聪电子网微信视频号

精彩评论