引言

众所周知,人在世界上生存需要空气、水和食物。那么MCU正常工作需要的最基本电路,也就是最小系统电路是什么呢?答案是电源电路、复位电路和时钟电路以及程序下载调试接口电路。今天我就结合NXP/Freescale的汽车级MCU来给大家详细介绍一下。

1.电源电路

电源电路是给MCU提供电源的电路,一般包括CPU内核电源(VDD/VCC)、模拟电路模块电源(VDDA)和数字逻辑外设、I/O接口电源(VDD)以及存储器(NVM-Flash--VDDF,DDRRAM--Vddr)电源等,具体根据不同的MCU和封装以及片上外设不同,其电源种类和数量也存在差异。

硬件设计tips:

a.一般对于每一个电源管脚,都需要设计一个0.1uF的去耦(decouple)电容并就近放在在MCU电源管脚附近(越近越好),以保证电源供电的稳定性和提高系统的EMC性能。下图为某一S12(X)系列16位MCU的电源电路PCBLayout推荐:

b.某些MCU内部集成的POR上电复位电路对VDD/VCC的去耦电容(容值大小和温漂一致性)选择有一定的要求满足其POR上电爬升斜率(rampslewrate)的要求。比如FreescaleS08RN系列MCU对电源PORre-arm的要求:

c.对于MCU的电源芯片选择,不但要考虑其供电能力(对于汽车电子应用,一般根据datasheet计算出MCU最大工作电流,留2~3倍裕量,在500mA以内的选择LDO即可,大于500mA的一般选择DC-DC)和还要考虑其不同电源的上电时序(对于复杂MCU,比如QorivvaMPC57xx系列多核MCU),需要根据具体的MCUdatasheet来选择和设计;

2.复位电路

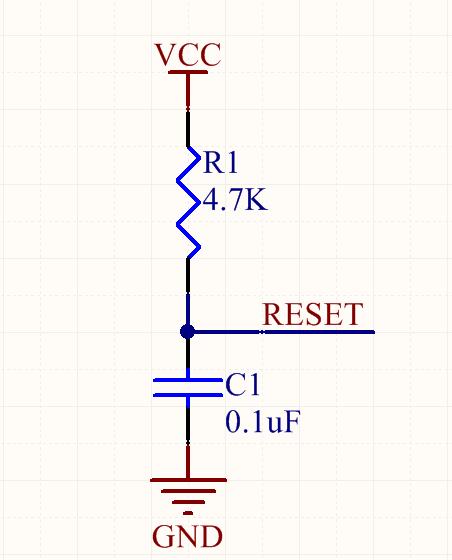

MCU一般都有一个RESET复位管脚,一般为低电平有效,其在MCU工作过程中时一个内部弱上拉的双向I/O,即可用通过在该管脚输入一个低电平啦对MCU进行系统复位,同时,当有内部系统复位(POR--上电复位、LVR--低电压检查复位、ClockMornitor/LostReset--时钟监测/丢失复位、WatchdogTimeoutReset--看门狗溢出复位和iligalAddress/InstructionReset--非法地址/指令复位等)产生时,其也将被拉低。所为复位电路就是接在RESET管脚上的外部电路,其要一般由一个上拉电阻(保证MCU正常工作时RESET管脚为高电平)和一个滤波电容(滤除外部干扰,增强MCU的抗干扰能力)组成,上拉电阻为4.7KΩ~10KΩ,电容为0.1uF~0.22uF.

典型的MCU复位电路如下:

硬件设计tips:

a.关于复位电路的上拉电阻和滤波电容大小的选择,需要根据具体的MCUPOR上电复位时序要求以及需要的滤波效果来确定;

b.当然,很多时候MCU的RESET管脚也与电源芯片的LVR输出管脚或者外部看门狗芯片的复位输出接在一些,这个时候就需要考虑:

电源芯片的LVR阈值和MCU本身的LVR阈值是否阈值,如果电源芯片的LVR阈值高于MCU的LVR阈值,那么MCU就无法正常进入LVI中断;

MCU上电之后需要及时对外部看门狗芯片进行喂狗,以防止其溢出复位,保证MCU正常工作;

3.时钟电路

MCU的CPU内核和数组逻辑外设都是以触发器为基础的时序电路,需要是中华驱动才能正常工作,所以时钟电路对于MCU来说就像心脏之于人的作用,给MCU提供“心跳”驱动,是十分重要的。虽然大多数MCU内部都集成了内部RC时钟(IRC)可以作为系统时钟使用,但其精度一般做不高,只有10%~1%精度,不能够满足一些高精度的定时器工作需要和高速通信外设的要求,比如汽车电子应用中常用的CAN总线。如果外设需要高精度的定时或者通信参考/同步时钟,这个时候就需要使用外部时钟作为系统时钟源了。

MCU复位之后,在外部时钟电路稳定之前,MCU默认使用内部时钟作为系统参考时钟源,直到用户通过软件配置将其切换为外部时钟源,外部时钟源电路才开始工作。外部时钟源,比如常见的无源晶振电路配合MCU内部的OSC电路一起工作,一般为正玄波信号,其频率高于内部参考时钟,所以其启动时间快,但相对功耗也高(mA级工作电流,内部参考时钟工作电流多为uA级),因此低功耗模式下,外部时钟源一般处于关闭状态,而内部时钟源用于唤醒源外设。

以下为NXP/Freescale汽车MCU的时钟资源对比:

MCU系列内部时钟源/精度外部时钟源

S08系列32.768KHzIRC/±2%4~20MHz无源晶振

1KHz低功耗LPO/~%

S12(X)系列1MHZIRC/±1.3%4~16MHz无源晶振/有源时钟(仅S12X系列MCU)

10KHZ低功耗自主时钟ACLK/±5%

MagniVs12Z系列1MHZIRC/±1.3%4~20MHz无源晶振

20KHZ低功耗自主时钟ACLK/±6%

QorivvaMPC56xx/57xx系列16MHzFIRC/±5%4~16MHz无源晶振/有源时钟和32~40KHzRTC晶振

128KHzSIRC/±10%

KEA系列32.768KHzIRC/±0.8%4~24MHz无源晶振(RANGE=0)或者31.25~39.0625KHzRTC晶振(RANGE=1)

1KHz低功耗LPO/~%

S32K系列48MHzFIRC/±1%4~40MHz无源晶振/有源时钟

8MHzSIRC/±3%

128KHzSIRC/±10%32.768KHzRTC晶振

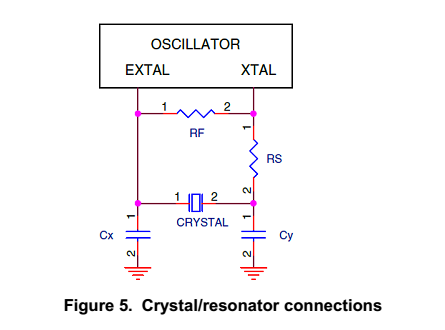

不同的MCU支持的外部时钟频率和类型有所差异,需要根据datasheet来选择和设计。典型的MCU外部无源晶振(crystal)时钟电路如下,Cx和Cy为负载(load)电容,也称为谐振电容,根据所选晶振频率的不同,一般在几pF~几十pF。RS和RF为时钟串联(serial)电阻和反馈(feedback)电阻,为可选期间。

硬件设计tips:

a.MCU的时钟(Oscillator)参数不同,一般在其datasheet的电气参数中给出,不同的晶振频率对于不同的启动时间,频率越高启动时间越短,但对外的EMC就越差,所以一般选择中间频率,然后通过内部时钟倍频模块(比如PLL)倍频到较高的MCU工作内核频率和总线频率;

b.在外部时钟电路设计时,为了提高其抗干扰能力建议:在外部晶振电路应该靠近MCU时钟管脚,走线越近越好,且外围覆铜包地。在时钟电路附件减少其他信号走线,特别是高数数字信号走线应该远离时钟电路以避免相互干扰。如下是一个推荐的MCU外部晶振时钟电路推荐PCBLayout:

C.在内部IRC时钟精度可以满足系统设计要求的情况下,尽量不要使用外部时钟。因为IRC时钟源不但功耗低,其对外的电磁辐射小、可干扰能力强,EMC特性好,同时也可以节省外部时钟电路的成本。

d.虽然MCU内部集成的PLL/FLL倍频单元可以将时钟倍频到datasheet规定的最大系统时钟和总线时钟频率,但在满足系统设计内核CPU计算速度和外设工作频率的情况下,尽量使用较低的系统时钟和总线时钟。一来可以降低对外的频率辐射,获得较好的EMC特性;二来可以降低MCU系统功耗(频率越高,时序逻辑电路的动态功耗也越大)。

4.程序下载和调试接口电路

MCU出厂之后默认的用户NVM--EEPROM和Flash中都是空白(全0xFF)的,包括其复位向量都是0xFF,必须要向NVM中下载应用程序,MCU才能正常工作。

不同的MCU,其程序下载和调试电路有所差异,常见的NXP/Freescale汽车级MCU的程序下载和调试接口如下表:

MCU系列程序下载和调试接口

S08系列BDM

S12(X)系列BDM

MagniVs12Z系列BDM

QorivvaMPC56xx/57xx系列JTAG/NEXUS

KEA系列SWD

S32K系列JTAG

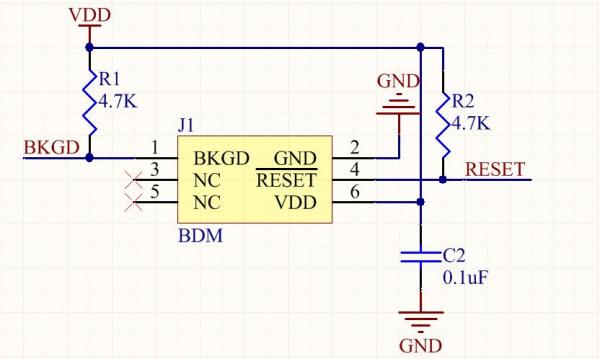

4.1.BDM接口

BDM--BackgroundDebugModule,背景调试接口是Freescale为其8位和16位MCU开的应用程序下载和调试接口。标准的BDM接口为6-pin,个管脚功能定义如下:

管脚(#)符号定义功能定义

1BKGDBDM协议同步信号和数据信号(双向通信)

2GND信号地

3NC/PDO悬空,不接/分析(Profiling)数据输出*

4RESET复位信号

5NC/PDOCLK悬空,不接/分析(Profiling)数据输出时钟*

6VDD目标MCU电源(输出--供电/输入--目标MCU上电检测)

*仅适用于MagniVS12Z系列MCU

典型的BDM接口电路如下:

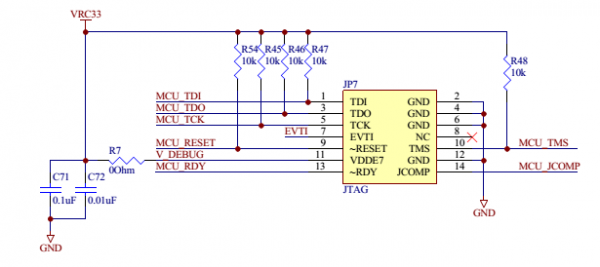

4.2.JTAG接口

JTAG--JointTestActionGroup--联合测试工作组,是一种国际标准测试协议(IEEE1149.1兼容),主要用于芯片内部测试。现在多数的高级器件都支持JTAG协议,如DSP、FPGA和32位MCU器件等。标准的JTAG接口4条JTAG功能信号线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线,具体定义如下表:

符号定义功能定义

TMS测试模式选择

TCK测试同步时钟

TDI测试数据输入(MCU-input,Debugger--output)

TDO测试数据输出(MCU-output,Debugger--input)

除了以上JTAG的标准功能信号线之外,其还需要配合电源VCC、地GND和复位信号RESET等才能组成完整的MCU程序下载和调试接口。

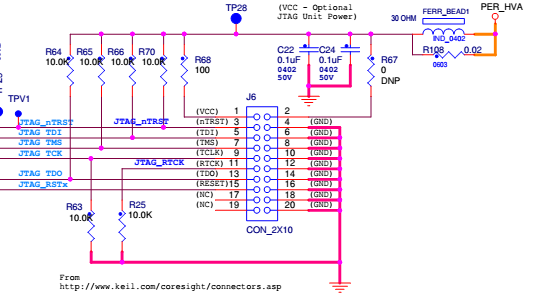

在32位MCU中常用的JTAG接口的连接有两种标准,即14针接口和20针接口,不同的系列/内核的MCU其定义稍有差异,以下列出NXP/Freescale32位汽车级MCU典型的JTAG电路供大家参考:

适用于QorivvaMPC56xx/57xx系列MCU的14-pinJTAG接口典型电路如下:

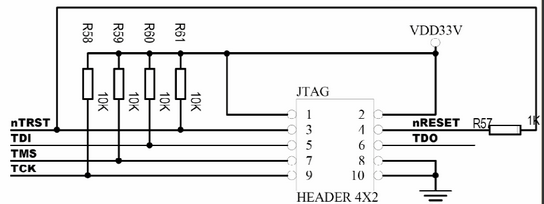

适合于ARMCortexM4F内核的S32K系列MCU和CortexA5内核的MAC57D5xx(Halo)系列MCU的20-pinJTAG典型电路如下:

除此之外,常用的还有10-pin的JTAG接口,其典型电路如下:

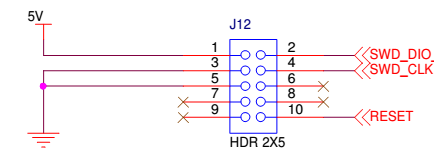

4.3.SWD接口

SWD--SingleWireDebug单线调试,是ARM推出针对其ARMCortexM系列内核的调试协议,其相较于传统的JTAG调试协议,接口信号线只有2根--单线时钟SWCLK和单线数据输入输出SWDIO,占用MCU的I/O更少,不但设计更加简单,在同样的封装下可提供更多的用户I/O,同时其又与JTAG接口兼容复用,如下表;

JTAGSWD功能定义

TMSSWDIO单线数据输入输出,用于控制信息数据和调试数据接收以及程序下载串行传输

TCKSWCLK单线时钟,用户通信同步

TDI未使用

TDO未使用

适合于ARMCortexM0+内核的KEA和ARMCortexM4F内核的S32K系列MCU的10-pinSWD典型电路如下:

硬件设计tips:

a.下载和调试接口电路应该靠近MCU放置,避免过长走线;

b.尽快BKGD和TMS、TCK、TDI及TDO在MCU内部有弱上电,但还是建议设计下载和调试接口电路在外部加上4.7K~10KΩ的上拉电阻,以保证其工作稳定;

c.建议在下载和调试接口电路的电源VDD/VCC管脚上加一个0.1uF的滤波电容,以保证电源的稳定;

总结

基于以上介绍,在在遇到上电后MCU不工作(无功能)时,我们就有了查找原因的思路如下:

首先,使用示波器查看MCU各电源是否稳定?

然后,检查RESET复位管脚是否为稳定的高电平?

接着,检查MCU时钟电路是否正常工作,外部晶振是否起振,频率和幅值是否满足datasheet要求?

最后,检查是否下载了正确的应用程序,以及程序下载和调试接口电路是否正常?

对于BDM接口,如果上电过程中,BKGD管脚为低电平,则S08/S12(X)MCU进入BDM调试模式,MCU是不会正常运行内部程序。

对于JTAG/SWD接口,TMS/SWDIO和TCK/SWCLK上的一系列脉冲信号也可能导致MCU进入debug模式,CPU内核和外设无法正常工作;

中微公司重组申请获上交所受理,或成科创板“简易审核程序”首单

中微公司重组申请获上交所受理,或成科创板“简易审核程序”首单 闪极170W超充站移动电源:细节设计见真章

闪极170W超充站移动电源:细节设计见真章 金天弘科技:全球新能源能效治理领域出货规模领先的传感器提供商

金天弘科技:全球新能源能效治理领域出货规模领先的传感器提供商 超越宇树!魔法原子300台机器人群控创行业记录

超越宇树!魔法原子300台机器人群控创行业记录

慧聪电子网微信公众号

慧聪电子网微信公众号

慧聪电子网微信视频号

慧聪电子网微信视频号

精彩评论