中国,上海—2018年3月1日—国际领先的定制化芯片(ASIC)设计方案提供商及DDR控制器和物理层IP供应商——灿芯半导体(上海)有限公司(以下简称“灿芯半导体”)日前对外宣布推出基于SMIC40LL工艺的第二代DDR低功耗物理层IP,该IP与第一代的低功耗DDRPHY相比面积减少20%,功耗减少37%,物理实现时间减少50%。

灿芯半导体推出第二代DDR低功耗物理层IP

第二代DDR低功耗物理层IP采用先进的双排IO结构,并采用了多项逻辑和物理的优化手段,延迟线面积减少20%,减少了每个DQ/DQS的时延误差,消除了之前物理实现的蛇形走线及每个DQ上不同数目的或者不同推力的缓冲器等问题,进而提高了硅利用率,提高了DDR的速度,并且减少了功耗。

第二代DDR低功耗物理层IP具有如下特性:

基于SMIC40LL工艺

支持DDR3/3L/3U/LPDDR31333Mbps,DDR2/LPDDR21066Mbps

支持PHYevaluationtraining或者softwaretraining模式

支持RDDQS下降沿training模式

支持AHB/APB3.0寄存器接口

“灿芯半导体具有10年的芯片设计经验和丰富的DDRIP技术积累,灿芯的YouPHY-DDRIP覆盖SMIC28HKMG、SMIC40LL、SMIC55LL、130nm等工艺,20多颗含有灿芯DDRIP的芯片成功流片,涉及DTV、AP、导航、SSD及NVDIMM等诸多应用领域,得到客户的充分肯定,”灿芯半导体首席技术官庄志青说,“我们将不断进行架构创新,提高服务质量,改进实现流程,从而为客户提供更有竞争力的解决方案。”

关于灿芯半导体

灿芯半导体(上海)有限公司,是一家国际领先的定制化芯片(ASIC)设计方案提供商及DDR控制器和物理层IP供应商,定位于55nm/40nm/28nm以下的高端系统级芯片(SoC)设计服务与一站式交钥匙(Turn-Key)服务。灿芯半导体为客户提供从源代码或网表到芯片成品的一站式服务,并致力于为客户复杂的ASIC设计提供一个高性价比、低风险的完整的芯片整体解决方案。

灿芯半导体由海内外的风险投资公司于2008年投资成立,2010年和中芯国际集成电路制造有限公司结盟成战略伙伴。公司总部位于中国上海,下设北京灿芯创智和合肥灿芯科技两家子公司,同时还在美国、欧洲、日本和台湾地区等地设立行销办事处提供客户服务。

中微公司重组申请获上交所受理,或成科创板“简易审核程序”首单

中微公司重组申请获上交所受理,或成科创板“简易审核程序”首单 闪极170W超充站移动电源:细节设计见真章

闪极170W超充站移动电源:细节设计见真章 金天弘科技:全球新能源能效治理领域出货规模领先的传感器提供商

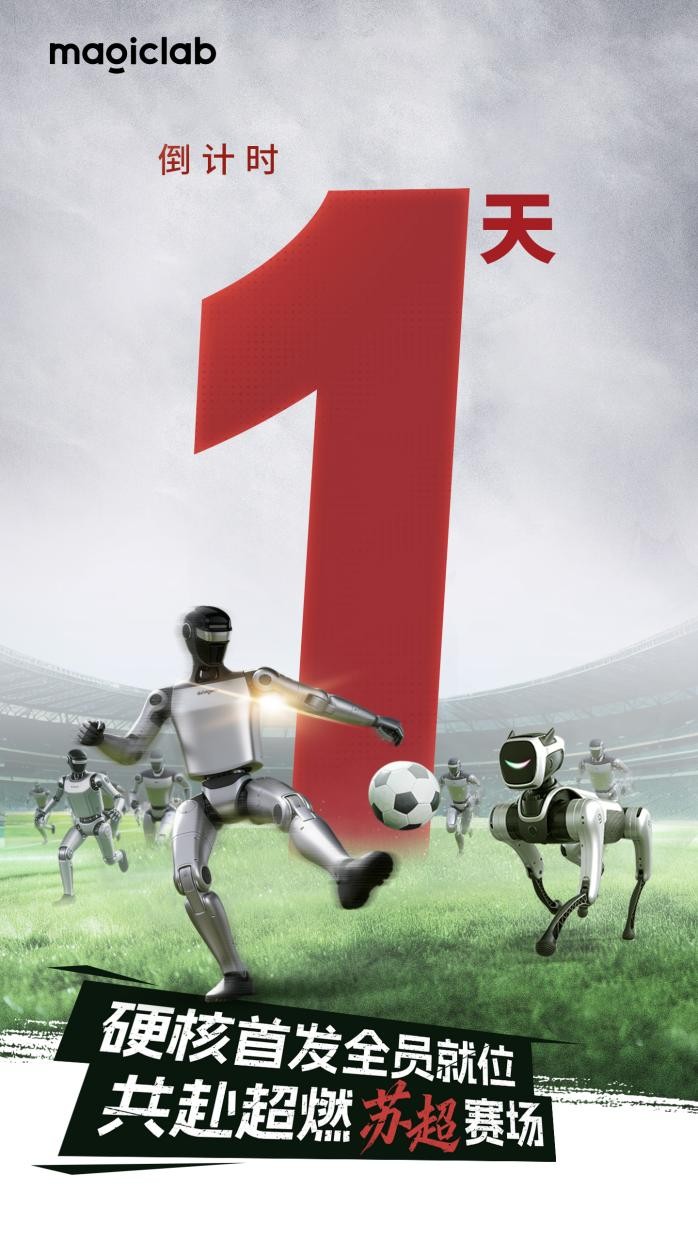

金天弘科技:全球新能源能效治理领域出货规模领先的传感器提供商 超越宇树!魔法原子300台机器人群控创行业记录

超越宇树!魔法原子300台机器人群控创行业记录

慧聪电子网微信公众号

慧聪电子网微信公众号

慧聪电子网微信视频号

慧聪电子网微信视频号

精彩评论