重点:

最新DesignWare56GEthernetPHY支持PAM-4和NRZ信号标准,适用于100G、200G和400GEthernet应用。

硅验证的可配置发射器和基于DSP的接收器以及模数转换器降低功耗并优化了性能。

高速PHY支持光缆和铜缆以及架顶交换机背板接口。

独特的可扩展PHY架构支持下一代800GEthernet应用112G接口。

2018年8月14日,中国北京——新思科技(Synopsys,Inc.,纳斯达克股票市场代码:SNPS)宣布,推出最新DesignWare®56GEthernetPHYIP,支持新兴400千兆/秒(Gbps)超大规模数据中心片上系统(SoC)。先进的56GEthernetPHY架构结合新思科技经硅验证的数据转换器,以及可配置发射器和基于数字信号处理器(DSP)的接收器,为目标应用实现最佳功效比。为满足叶脊架构带宽要求,PHY支持10G到400GEthernet单链路和聚合链路速率,同时满足PAM-4和NRZ信号标准。此外,PHY性能超过了OIF和IEEE芯片到芯片、背板和铜/光缆接口标准性能要求。新思科技56GEthernetPHY、数字控制器、验证IP与源代码测试套件相结合,为设计师开发网络数据中心系统提供完整的EthernetIP解决方案。

56GEthernetPHY眼图

为提高时序恢复和防时钟抖动性能,56GEthernetPHY接收器采用多回路时钟数据恢复电路以及全功能DSP。独特的PAM-4发射器架构支持精确前馈均衡,满足信道性能要求。56GEthernetPHY可扩展架构为需要112G连接的下一代800GEthernet应用奠定了基础。

新思科技解决方案集团产品市场副总裁JohnKoeter表示:“数据中心所需带宽不断提高增加了网络基础设施的工作负荷。新思科技DesignWare56GEthernetIP使设计师能够满足400G超大规模数据中心SoC高性能Ethernet连接要求,同时降低风险。“

供货情况及其他信息资源

采用16nm和7nmFinFET工艺技术的DesignWare56GEthernetPHY硅设计套件将分别于2018年第3季度和2018年第4季度上市。

欲了解更多信息,请访问DesignWare56GEthernetPHYIP、DesignWareEthernetIPSolutions和VCVerificationIPforEthernet网页。

超越宇树!魔法原子300台机器人群控创行业记录

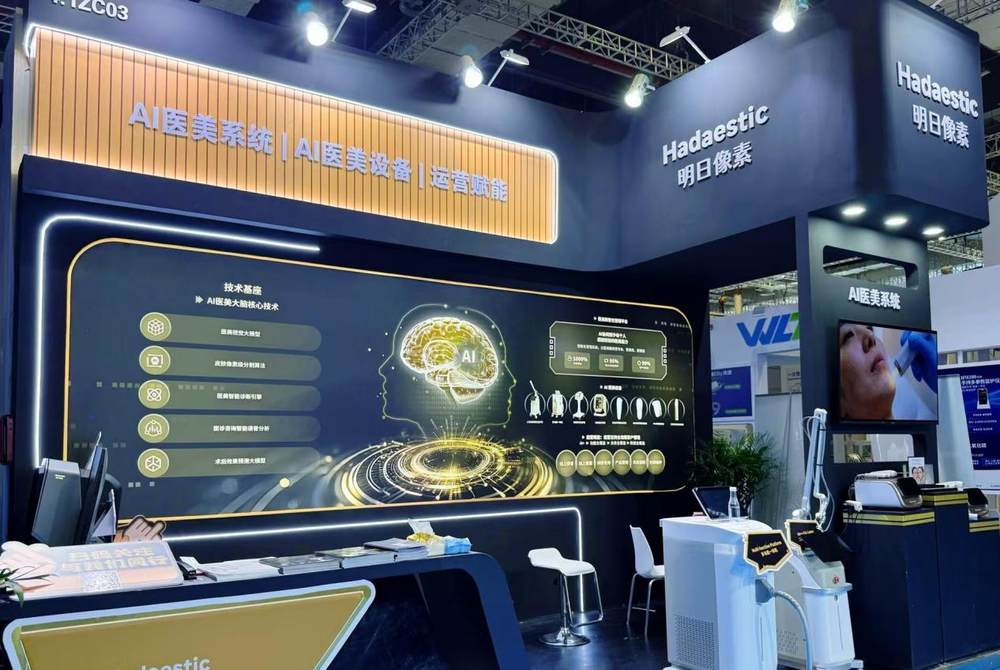

超越宇树!魔法原子300台机器人群控创行业记录 明日像素携 “AI 医美大脑” 亮相 2026 CMEF

明日像素携 “AI 医美大脑” 亮相 2026 CMEF ESIS 2026第六届中国电子半导体华南数智峰会报名通道正式开启!

ESIS 2026第六届中国电子半导体华南数智峰会报名通道正式开启! ESIS 2026第五届中国电子半导体数智峰会完美收官,亮点回望!

ESIS 2026第五届中国电子半导体数智峰会完美收官,亮点回望!

慧聪电子网微信公众号

慧聪电子网微信公众号

慧聪电子网微信视频号

慧聪电子网微信视频号

精彩评论