半个世纪前,英特尔创始人之一戈登·摩尔提出“摩尔定律”(Moore's Law),从这以后,芯片厂商们多遵从这一定律生产芯片。而近年来,“摩尔定律”被其他厂商唱衰,本该是芯片“鼻祖”的英特尔也在技术上渐渐落后于竞争对手。在此次的架构日,英特尔展示了他们的众多下一代技术和已经做出的创新,其中就包括业界首个3D堆叠逻辑芯片。

据媒体报道,12月11日,英特尔召开架构沟通会。会上,英特尔向参会者介绍了其基于10nm的PC、数据中心和网络系统,并分享了其在处理器、架构、存储、互连、安全和软件等六个工程领域的技术战略。其中,热度最高的莫过于新开发的首个3D封装架构“Foveros”,它可以说是英特尔面对其他从业者质疑“摩尔定律”的最好回应。

近年来多次出现“摩尔芯片唱衰论”。用很小的体积做到高性能,是现在芯片技术的主要方向,但是又要小,又要做到性能高,厂商们若再运用“摩尔定律”制造芯片,无疑难度很大。如今制作芯片的困难主要来自于材料上,当芯片制程达到10nm时,栅氧化层的厚度变薄,会产生诸多量子效应,晶体管很容易漏电。当其他厂商接连研制出10nm、7nm制程的芯片时,一直使用“摩尔定律”的英特尔反而把本该在今年7月份就宣布发布的10nm制程工艺推迟到了明年年末。

而此次推出的Foveros技术则是对“摩尔定律”的延续。英特尔表示,Foveros可以做到将计算电路堆叠,并快速地将它们连接到一起,从而将更多的计算电路组装到单个芯片上,实现高性能、高密度和低功耗。

2019年下半年,英特尔将开始使用Foveros推出一系列产品,其首款产品将结合高性能10nm计算堆叠小芯片和低功耗22FFL基础芯片。

英特尔芯片架构主管拉贾·科杜里(Raja Kosuri)表示,他们在这20年里,一直研究这项技术。堆叠以前曾在内存芯片中使用,但英特尔是第一家将该技术应用到所谓的“逻辑”芯片中的公司。

“落后”的英特尔,这次要走在前面了。

中微公司重组申请获上交所受理,或成科创板“简易审核程序”首单

中微公司重组申请获上交所受理,或成科创板“简易审核程序”首单 闪极170W超充站移动电源:细节设计见真章

闪极170W超充站移动电源:细节设计见真章 金天弘科技:全球新能源能效治理领域出货规模领先的传感器提供商

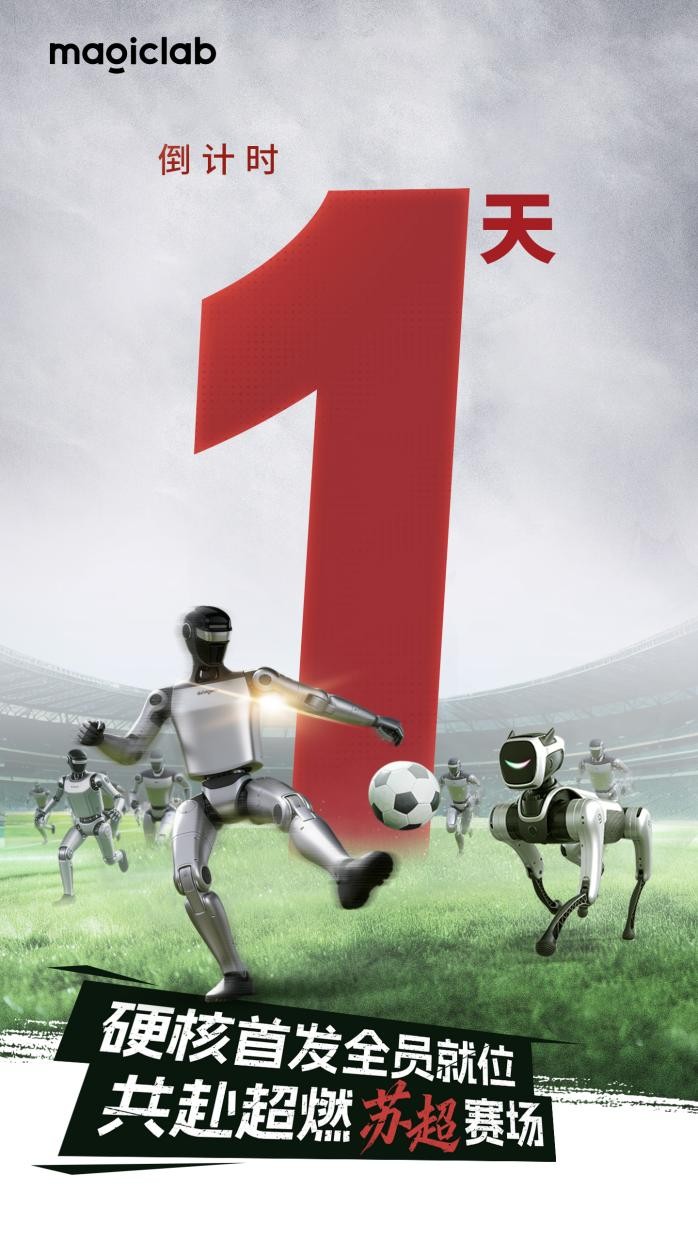

金天弘科技:全球新能源能效治理领域出货规模领先的传感器提供商 超越宇树!魔法原子300台机器人群控创行业记录

超越宇树!魔法原子300台机器人群控创行业记录

慧聪电子网微信公众号

慧聪电子网微信公众号

慧聪电子网微信视频号

慧聪电子网微信视频号

精彩评论