加速汽车IC设计周期

自动驾驶汽车(AV)正在将我们推入一个全新的移动时代,为了满足AV的高性能和低功耗要求,如今的SoC设计者需要为AI算法优化定制的硅架构,使用传统的设计方法十分耗费时间,于是HLS(高等级逻辑综合)开始步入人们眼帘。

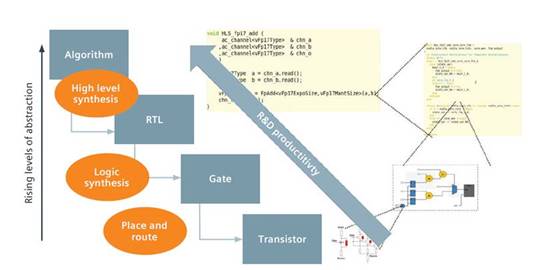

HLS能够使用SystemC或C++对设计功能进行高级描述,并将它们综合到RTL中。在更高抽象层次上进行设计,通过将芯片功能规约与实现规约相分离,加速初始设计的完成(图1)。这种方式能将设计时间缩短至几个月,所需代码仅是传统RTL流程的一半。在不影响设计进度的情况下,后期的功能变化、新特性,甚至跨节点合并、从FPGA到ASIC的转换均可被集成。HLS还能帮助设计团队探索数百种设计变体,进而优化芯片的功率、性能及面积。与手工编码的RTL相比,DSE(设计空间探索)能够以此获得更高的设计质量。

如果仿真被合并到该流程当中,设计就会进一步加速。HLS生成的RTL可以在仿真器中被具象化,为软件团队提供一个在芯片硬件可用之前先测试软件的平台;同时,综合传感器和机电系统的数据也将被集成,创建能够提供真实反馈的虚拟环境,帮助团队优化硬件和软件设计。

图1:HLS提高了设计抽象级别以提高设计生产力

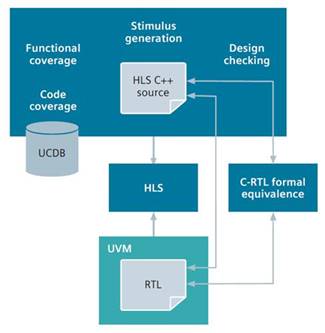

最后,先进的HLS解决方案将对设计进行稳健性验证,方便设计人员在RTL之前就消除错误(图2)。HLS的验证能力包括对C++或SystemC代码的自动形式化检查、基于仿真的C-RTL验证和形式等效性检查,在综合到RTL之前就可以发现缺陷和错误。

图2:先进的HLS可以在RTL之前执行C-to-RTL验证以删除缺陷和错误

功能安全、验证以及安全设计

功能安全是指降低电气和电子元件因故障而运转失常的风险。在汽车工业中,这些程序和要求已在ISO26262标准中被正式提出,该标准还同时要求对电子设备进行随机硬件故障和系统故障测试。

一个完整的功能安全流程中通常包括四个关键步骤(图3)。

1.生命周期管理,涵盖从计划到合规的功能安全生命周期。

2.安全分析使用FMEDA来了解随机硬件错误导致的设计潜在失效模式。

3.安全设计尝试增强或修改设计,以减轻随机硬件错误带来的潜在失效。

4.安全验证使用故障注入测试设计和安全机制在随机硬件错误中的行为,最终证明该设计的安全性。

如今,先进的解决方案组合(如MentorSafeIC)能够实现严格的功能安全标准,同时自动化生命周期管理、安全分析、安全设计和安全验证过程,加快了功能安全的验证速度,使其尽快符合行业标准。

图3:功能安全的四个关键过程:生命周期管理、安全分析、安全设计和安全验证

仿真在验证中的作用

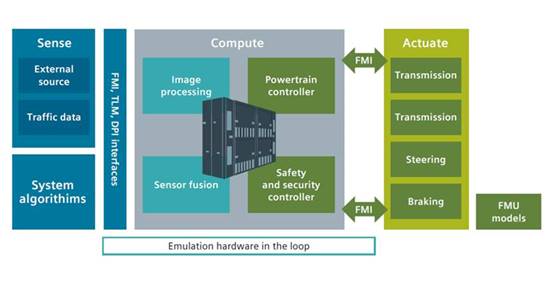

在现实世界中测试所有可能的安全场景并不可行,要实现大量验证的唯一方法就是在设计初期使用虚拟测试环境。硬件仿真支持模型以及软件和硬件的在环验证,都在芯片或车辆硬件可用前提供了一个能够进行测试、编程和调试IC或整车平台的环境,主要涵盖下图中三种数据类型(图4)。

图4:硬件仿真可以融合传感器、计算和驱动数据,为AV平台创建测试环境。

物理可靠性验证

SoC设计团队已经通过HLS支持的快速迭代对芯片进行了优化,验证了芯片的功能性和功能安全性,并在真实的虚拟驾驶环境中用模拟传感器和机电数据对芯片进行了测试。

新的IC可靠性验证工具能够在一个内聚环境中考虑有问题的区域。这些工具是为了在电路感知环境下提高IC可靠性验证的覆盖率而创建的,它们允许从电路拓扑和布局的角度集中分析电路的实现方式。该分析还可以利用外部约束来确定检查目的,并找出不合规的电路。

接下来,设计师需要优化芯片的物理布局。DFM(可制造性设计)解决方案能通过自动优化布局、模拟制造过程或在tape-out前管理光刻热点来帮助设计师,其可以自动测量由建议的布局修改引起的产量变化,使得设计者能够选择布局修改的方式,进而最大 限度地提高芯片的生产效率和可靠性。

当数字“遇上”模拟

一辆AV的复杂数字处理器和控制器SoC将通过各种传感器系统与模拟世界进行交互。微机电系统(MEMS)通常用于传感装置,其余电路作为模拟/混合信号(AMS)设计,则采用CMOS工艺实现。

与使用现成的组件创建系统相比,定制化的IC设计能够帮助公司降低成本、控制尺寸和功耗。然而,由于涉及的设计领域众多,AMS设计提出了严苛挑战,MEMS设计必须与模拟电路有效地接口,而模拟电路又必须与模数转换器和数字逻辑相互集成。

汽车AMS集成电路必须以极强的可靠性持续运行,且大多数时间都处于恶劣的环境条件。为了便于管理,设计师需要一个集成的设计和验证解决方案,该解决方案能够连接模拟、数字和MEMS,帮助创建AV最 重要的单用途智能传感器系统。

老化模拟在汽车应用中也非常重要。随着时间的推移,汽车应用的压力偏差和热状态会导致电路退化。通过仿真,可以及早发现潜在的可靠性问题,并在设计阶段加以纠正。

确保从始至终的安全性

新的汽车级ATPG技术将目标对准于晶体管和栅极级别的缺陷。这些新方法基于单元感知测试(CAT),使用专为每个单元内部缺陷而设置的故障模型。Mentor的CellModelGen故障特征模型提取使用单元的布局注释Spice表示来识别可能的晶体管、电桥、开路和端口缺陷的位置。通过计算每个潜在缺陷的临界面积及其相关的缺陷概率,分析潜在缺陷的单元布局。同时,该分析还能够生成一个模型,尽可能进行缺陷检测,最小化模式计数并保留诊断所需的信息。捕捉这些本不可检测的缺陷有助于数字集成电路IC制造商达到ISO26262的DPPB目标。

内建自测试(BIST)将测试IP插入芯片中,用于测试数字逻辑或存储器。逻辑BIST涉及到应用于芯片电路的片上生成伪随机测试模式。先进的测试解决方案能够在芯片运行期间进行测试,而不会影响其性能;此外,ATPG压缩可与BIST相集成,以进行用于通电和系统内测试的制造质量测试。

今天,无论是汽车初创企业、老牌OEMs还是系统公司都在争先恐后地进入市场,它们亟需一系列先进的设计自动化和生命周期管理工具。西门子数字化工业软件可以提供独特的工具组合,在HLS、功能安全和验证、仿真、物理可靠性验证、AMS设计、混合信号验证和IC测试方面拥有领 先的解决方案,帮助企业乘风破浪,在市场浪潮中立于不败之地。

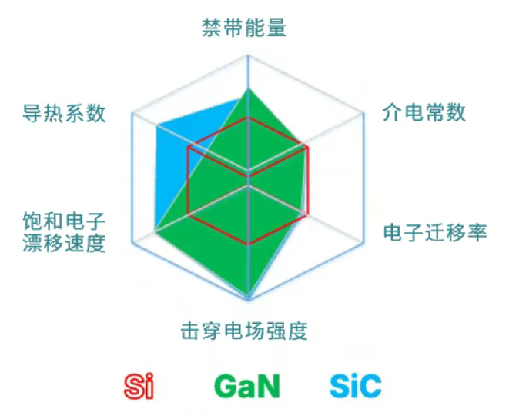

碳化硅赋能浪潮教程:SiC JFET驱动工业与服务器电源革新

碳化硅赋能浪潮教程:SiC JFET驱动工业与服务器电源革新 【首发】上海晶珩发布树莓派CM5龙虾盒子!要知道,你离AI私有化只差一个盒子!

【首发】上海晶珩发布树莓派CM5龙虾盒子!要知道,你离AI私有化只差一个盒子! 腾讯云TVP走进银河通用×NVIDIA×福田戴姆勒,解码AI驱动产业硬核突围之路

腾讯云TVP走进银河通用×NVIDIA×福田戴姆勒,解码AI驱动产业硬核突围之路 OpenClaw + 树莓派全栈部署手册:上海晶珩整理的最全避坑指南!

OpenClaw + 树莓派全栈部署手册:上海晶珩整理的最全避坑指南!

慧聪电子网微信公众号

慧聪电子网微信公众号

慧聪电子网微信视频号

慧聪电子网微信视频号

精彩评论