VCO,是一个频率随电压变化的部件,而变容管则是产生该频率变化的核心。在VCO的各项性能中,有两个性能,分别为频率的调谐范围和输出信号的相噪。这两项性能,则对应变容管的两个特性:(1) 电容的调谐范围,即变容管能提供的最大电容和最小电容;(2)变容管的品质因数(qulity factor),这个通常受变容管的寄生级联电阻限制。这两个参数,在某些情况下,是一个矛盾的关系。

在以前的RFIC设计中,变容管是用反偏的PN结实现。但在现在RFIC设计中,MOS变容管已经取代了PN结,成为主流。

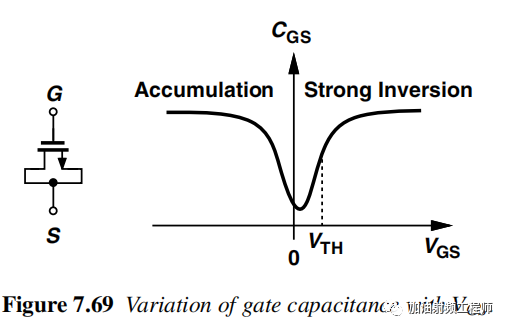

常规的MOSFET在将D极和S极连接时,Cgs与Vgs的关系如下图所示,Cgs会随着Vgs变化,但是变化曲线呈现非线性。这个非线性,会产生这样一个结果。比如说,你设计了一个VCO,当你缓慢升高电压时,它的输出频率也相应地从1G变到2G。但是由于这个非线性的存在,当你缓慢升高电压时,刚开始频率是1G变化到1.5G;然后你在缓慢升高电压,发现频率又缓慢变回去了。当然,也不是完全不能用,但是总觉得心里有那么点不舒服。

而且,这种非线性的频率调谐特性,在锁相环设计中是个问题,会使得锁相环失锁。

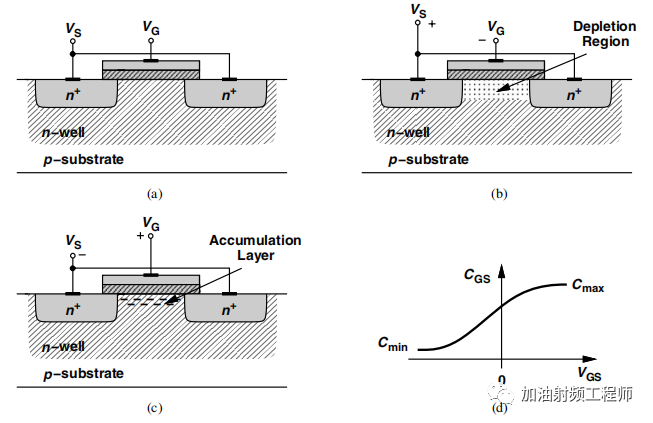

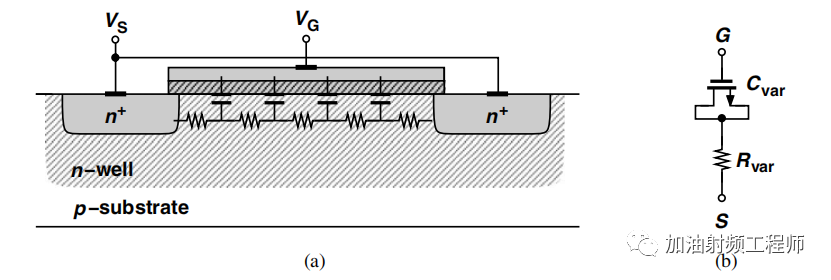

那怎么办?解决办法,就是对MOS管做一个小小的调整,具体方法,就是把NMOS管放在一个N阱中,这种MOS管,称为“累积型MOS变容二极管(Accumulation-mode MOS varacotr)”。

当VG<VS时,N阱中的电子从硅/氧化物的交接面被排斥出来,使得交接面处形成耗尽区。所谓耗尽区,就是其区域不存在自由移动的载流子,产生类似电容的特性。因此,此时的等效效电容为栅氧电容和耗尽电容的串联。当VG>VS时,硅/氧化物的交接面从n+的源极和漏极吸收电子,形成一个通道。此时,等效电容为栅氧电容。

在65nm器件中, VGS ≈ ±0.5 V时,接近其饱和水平的Cmax和Cmin。MOS变容二极管可以在低供电电压下工作,而且,为了使得MOS管提供最大的调谐特性,MOS管需要正负偏置。

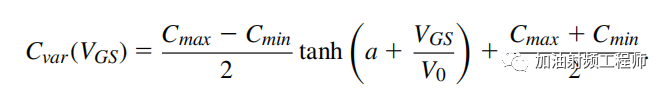

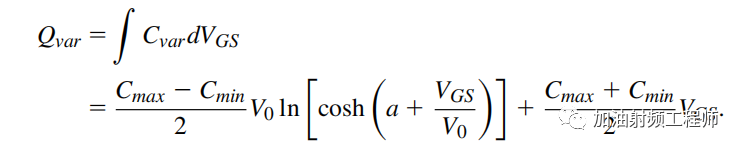

电路仿真,需要在一定程度上能够模拟变容管的C/V特性曲线。在实际中,这种特性是对加工器件进行测量,然后以由一系列的离散值组成的表格来表征。然后,再用一个连续函数来对C/V曲线进行拟合。双曲正切能够很好地模拟其饱和特性,具有连续导数,因此可以用来拟合C/V曲线。

其中a和V0分别允许拟合截点和斜率,而Cmin和Cmax则包含栅漏和栅源的重叠电容。

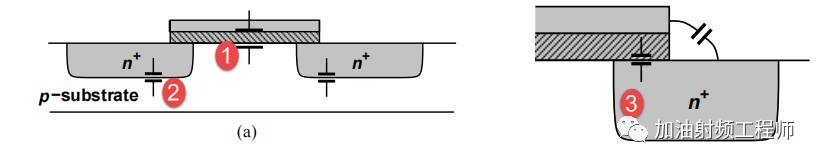

什么是重叠电容呢(overlap capacitance)?

如上图所示,MOS管有三种主要电容:

一种是栅极和沟道之间的电容,称为栅氧电容,值为WLCox;

一种为源极和衬底,漏极和衬底之间的PN结电容;

一种为重叠电容(overlap capacitance)。

在加工过程中,会使得栅极和漏极,栅极和源极在结构上部分重叠;另外栅极边缘与源极/漏极区域顶部之间的边缘场线,这两者构成了重叠电容。

上述C/V模型,也可转换成Q/V模型,即电荷随电压变化的曲线。

由dQ=C(V)/dV可知,

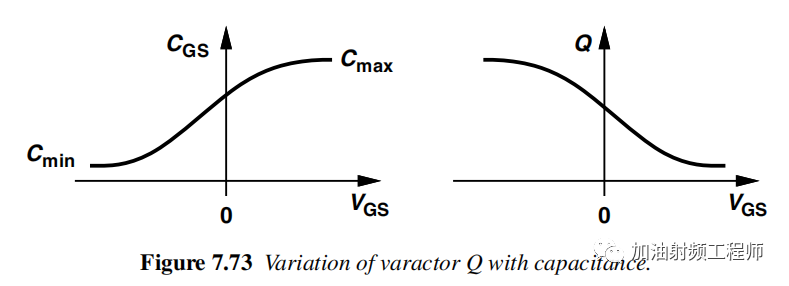

MOS变容管的Q值,由栅极和漏极之间的电阻决定,如下图所示。

MOS变容管的Q值又是如何变化的呢?当变容管的容值为Cmin时,其容值低,电阻又比较大;而当变容管的容值为Cmax时,其容值大,而电阻又比较低。由Q=1/(RCw)可知,Q如果按照上述规律变化的话,可能能够保持不变。实际上,当Cgs从Cmin变化到Cmax时,Q值也是下降的。这表明,当Cgs从Cmin变大到Cmax时,R也会从Rmax变化Rmin,但是显然C的变化量要大于R的变化量。

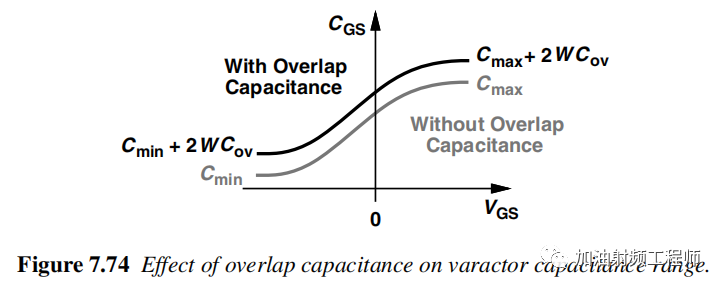

在振荡器设计中,希望最大化变容管的Q值。当沟道长度最短的时候,变容管的Q值最大;但是,此时栅源和栅漏之间的重叠电容在总电容中所占比值增大,从而限制了电容的调谐范围。重叠电容(overlap capacitance)基本上不太随电压变化,它的存在,会使得变容管的特征曲线上移,即从Cmin+2WCov变化到Cmax+2WCov。当沟道长度最短的时候,2WCov甚至会比Cmin还大。因此会降低电容的调谐范围。

具体用数字来表征一下:假设, Cmax=0.85fF,Cmin=0.18fF,此时R=Cmax/Cmin=4.72;如果考虑重叠电容,假设其值为0.18fF,则Cmax=0.18fF+0.85fF=1.03fF,Cmin=0.18fF+0.18fF=0.36fF,此时R=Cmax/Cmin=2.86。调谐范围下降。

因此,沟道长度短,变容管Q值大,但是电容的调谐范围相对较小。变容管Q值和调谐范围之间的矛盾,反应到VCO的性能上,就是频率调谐范围和相噪的矛盾。在实际的设计中,需要折中取舍。

晶圆代工大厂近59亿元收购案获批

晶圆代工大厂近59亿元收购案获批 罗姆为英伟达800V HVDC架构提供高性能电源解决方案

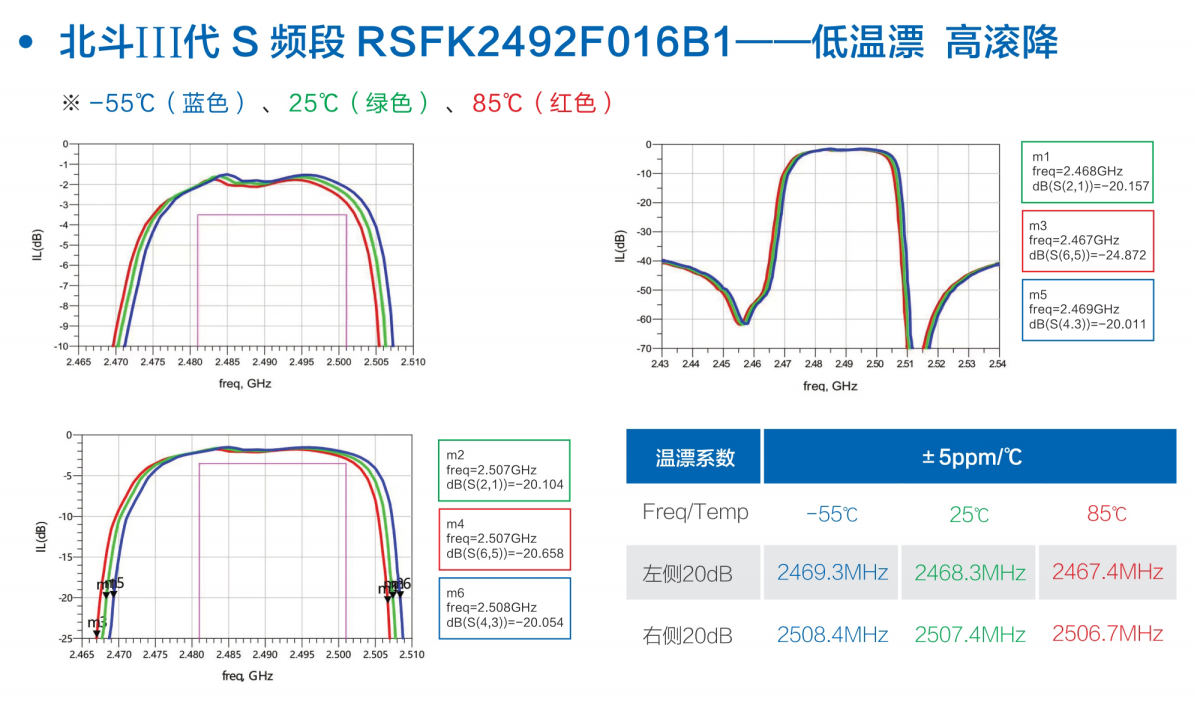

罗姆为英伟达800V HVDC架构提供高性能电源解决方案 诺思 “零温漂” 滤波器:技术创新赋能产业发展,知识产权护航行业未来

诺思 “零温漂” 滤波器:技术创新赋能产业发展,知识产权护航行业未来 DeepSeek引爆AI芯片需求,晶科鑫SJK差分晶振赋能服务器交换机

DeepSeek引爆AI芯片需求,晶科鑫SJK差分晶振赋能服务器交换机

慧聪电子网微信公众号

慧聪电子网微信公众号

慧聪电子网微信视频号

慧聪电子网微信视频号

精彩评论