电路设计软件越来越重要,因此学习电路设计软件的人数越来越多。为增进大家对电路设计软件的了解,本文将从多个方面对电路设计软件protel予以讲解,主要内容在于阐述如何在电路设计软件protel中新建原理图文档、protel元器件间距和安装尺寸探讨,以及介绍Protel到Allegro转化的方法。

一、protel如何新建(创建)原理图文档

PROTEL如何创建新的原理图(SCH)文档呢,这是初学PROTEL需要学习的课题。下面我来详细讲解一下步骤及流程。

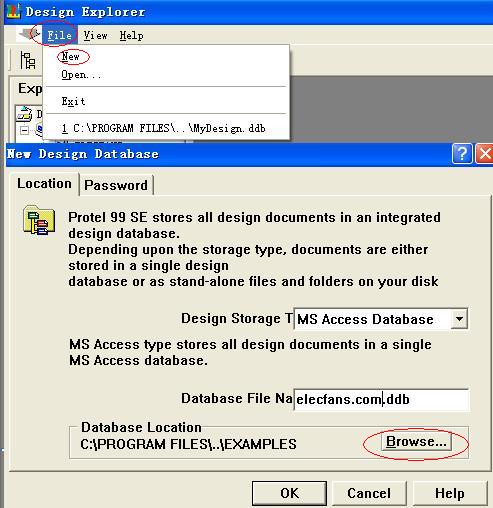

第一:file--new---目录设置

如上图,Browse处,可以自已设置想要创建文档的路径。

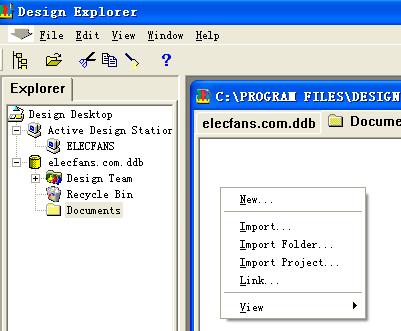

第二步:在如下图的"Documents"里头,右键---"new"

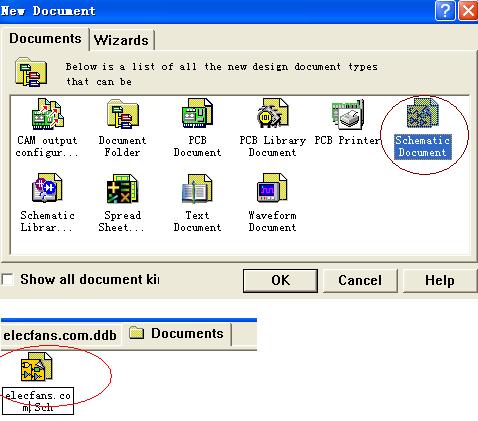

第三步:选择你要创建的文档,可以是SCH,PCB,Library,report,txt等文档。

如上图的位置还可以原理图更改名称。

二、protel设计之元器件的间距与安装尺寸

(1)元器件的引脚间距

元器件不同,其引脚间距也不相同。但对于各种各样的元器件的引脚间距大多都是:100mil(英制)的整数倍(1mil=l&TImes;10(-3立方)in=25.4&TImes;10(-6次方)m),常将100mil作为1间距。

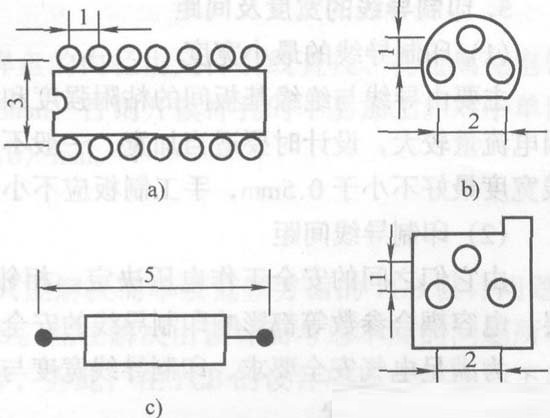

在PCB设计中必须准确弄清元器件的引脚间距,因为它决定着焊盘放置间距。对于非标准器件的引脚间距的确定最 直接的方法就是:使用游标卡尺进行测量。常用元器件的引脚间距如图所示。

常用元器件的引脚间距

a)DIPICb)TO-92型三极管c)1/4w型电阻器d)某微调电阻

(2)元器件的安装尺寸

是根据引脚间距来确定焊孔间距。它有软尺寸和硬尺寸之分。软尺寸是基于引脚能够弯折的元器件,故设计该类器件的焊接孔距比较灵活;而硬尺寸是基于引脚不能弯折的元器件,其焊接孔距要求相当准确。设计PCB时,元器件的焊孔间距的确定可用CAD软件中的标尺度量工具来测量。

三、99se之PLD设计

ProtelAdvancedPLD是融合于Protel集成开发环境的一个高效、通用的可编程逻辑器件设计工具,为逻辑器件设计提供了许多方便快捷的设计手段。

ProtelAdvancedPLD包含三个专为PLD设计工作定制的EDA/Client服务器:文本专家─具有语法认识功能的文本编辑器;PLD─用来编译和仿真设计结果;Wave─用来观察仿真波形。

具体特点如下:

.方便的文本专家和语法帮助器;

.支持多种设计描述方法:布尔方程式、状态机和真值表;

.支持从原理图输入并直接编译;

.支持从原理图输入PLD设计,并对原理图直接进行编译,生成标准的JEDEC文件;

.与器件无关的高级CUPL硬件描述语言;

.快速强大的编译器;

.方便直观的仿真波形编辑器;

.产生JEDEC工业标准的下载文件;

.广泛的器件支持。

四、Protel到Allegro转化的方法

在这过程当中碰到的问题大致可分为两种:一是设计不很复杂,设计师只想借助CadenceCCT的强大自动布线功能完成布线工作;二是设计复杂,设计师需要借助信噪分析工具来对设计进行信噪仿真,设置线网的布线拓扑结构等工作。

对于第一种情况,要做的转化工作比较简单,可以使用Protel或Cadence提供的Protel到CCT的转换工具来完成这一工作。对于第二种情况,要做的工作相对复杂一些,下面将这种转化的方法作一简单的介绍。

Cadence信噪分析工具的分析对象是CadenceAllegro的brd文件,而Allegro可以读入合乎其要求的第三方网表,Protel输出的Telexis格式的网表满足Allegro对第三方网表的要求,这样就可以将Protel文件注入Allegro。

首先,Allegro第三方网表在$PACKAGE段不允许有“.”;其次,在Protel中,我们用BasName[0:N]的形式表示总线,用BasName[x]表示总线中的一根信号,Allegro第三方网表中总线中的一根信号的表示形式为BasNameX,读者可以通过直接修改Protel输出的Telexis网表的方法解决这些问题。

Allegro在注入第三方网表时还需要每种类型器件的设备描述文件Device.txt文件,它的格式如下:

Package:packagetype

Class:classtype

Pincount:totalpinnumber

Pinused:。..

其中常用的是PACKAGE,CLASS,PINCOUNT这几项。PACKAGE描述了器件的封装,但Allegro在注入网表时会用网表中的PACKAGE项而忽略设备描述文件中的这一项。CLASS确定器件的类型,以便信噪分折,Cadence将器件分为IC,IO,DISCRETE三类。PINCOUNT说明器件的管脚数目。对于大多数器件,Device.txt文件中包含有这三项就足够了。

有了第三方网表和设备描述文件,我们就可以将Protel中原理图设计以网表的形式代入到CadencePCB设计软件中,接下来,设计师就可以借助CadencePCB软件在高速高密度PCB设计方面的强大功能完成自己的设计。

如果已经在Protel作了PCB布局的工作,Allegro的script功能可以将Protcl中的布局在Allegro中重现出来。在Protel中,设计师可以输出一个Place&Pick文件,这个文件中包含了每个器件的位置、旋转角度和放在PCB顶层还是底层等信息,可以通过这个文件很方便的生成一个Allegro的script文件,在Allegro中执行这个script就能够重现Protel中的布局了,下面给出了完成Place&Pick文件到AllegroScript文件转化的C++代码,笔者使用这段代码,仅用了数分钟就将一个用户有800多个器件的PCB板布局在Allegro重现出来。

全新OptoTEC®MSX多级热电制冷器可提供超紧凑设计,实现真空中高达100至120°C温差

全新OptoTEC®MSX多级热电制冷器可提供超紧凑设计,实现真空中高达100至120°C温差 Altera Agilex 3/5 FPGA和SoC的功能特性

Altera Agilex 3/5 FPGA和SoC的功能特性 大模型实战课:用Lattepanda Sigma开发板实现语音控制灯光

大模型实战课:用Lattepanda Sigma开发板实现语音控制灯光

慧聪电子网微信公众号

慧聪电子网微信公众号

慧聪电子网微信视频号

慧聪电子网微信视频号

精彩评论