PCI-Express(peripheralcomponentinterconnectexpress)是一种高速串行计算机扩展总线标准,它原来的名称为“3GIO”,是由英特尔在2001年提出的,旨在替代旧的PCI,PCI-X和AGP总线标准。

PCIe属于高速串行点对点双通道高带宽传输,所连接的设备分配独享通道带宽,不共享总线带宽,主要支持主动电源管理,错误报告,端对端的可靠性传输,热插拔以及服务质量(QOS)等功能

下面是关于PCIEPCB设计的规范:

1、从金手指边缘到PCIE芯片管脚的走线长度应限制在4英寸(约100MM)以内。

2、PCIE的PERP/N,PETP/N,PECKP/N是三个差分对线,注意保护(差分对之间的距离、差分对和所有非PCIE信号的距离是20MIL,以减少有害串扰的影响和电磁干扰(EMI)的影响。芯片及PCIE信号线反面避免高频信号线,最 好全GND)。

3、差分对中2条走线的长度差最 多5MIL。2条走线的每一部分都要求长度匹配。差分线的线宽7MIL,差分对中2条走线的间距是7MIL。

4、当PCIE信号对走线换层时,应在靠近信号对过孔处放置地信号过孔,每对信号建议置1到3个地信号过孔。PCIE差分对采用25/14的过孔,并且两个过孔必须放置的相互对称。

5、PCIE需要在发射端和接收端之间交流耦合,差分对的两个交流耦合电容必须有相同的封装尺寸,位置要对称且要摆放在靠近金手指这边,电容值推荐为0.1uF,不允许使用直插封装。

6、SCL等信号线不能穿越PCIE主芯片。

合理的走线设计可以信号的兼容性,减小信号的反射和电磁损耗。PCI-E总线的信号线采用高速串行差分通信信号,因此,注重高速差分信号对的走线设计要求和规范,确保PCI-E总线能进行正常通信。

PCI-E是一种双单工连接的点对点串行差分低电压互联。每个通道有两对差分信号:传输对Txp/Txn,接收对Rxp/Rxn。该信号工作在2.5GHz并带有嵌入式时钟。嵌入式时钟通过消除不同差分对的长度匹配简化了布线规则。

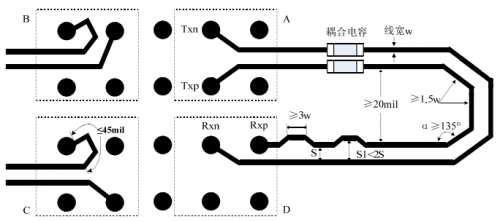

随着PCI-E串行总线传输速率的不断增加,降低互连损耗和抖动预算的设计变得格外重要。在整个PCI-E背板的设计中,走线的难度主要存在于PCI-E的这些差分对。图1提供了PCI-E高速串行信号差分对走线中主要的规范,其中A、B、C和D四个方框中表示的是常见的四种PCI-E差分对的四种扇入扇出方式,其中以图中A所示的对称管脚方式扇入扇出效果最 好,D为较好方式,B和C为可行方式。接下来本文将对PCI-ELVDS信号走线时的注意事项进行总结:

图1PCI-E差分线布线规范

(1)对于插卡或插槽来说,从金手指边缘或者插槽管脚到PCI-ESwitch管脚的走线长度应限制在4英寸以内。另外,长距离走线应该在PCB上走斜线。

(2)避免参考平面的不连续,譬如分割和空隙。

(3)当LVDS信号线变化层时,地信号的过孔应放得靠近信号过孔,对每对信号的一般要求是至少放1至3个地信号过孔,并且永远不要让走线跨过平面的分割。

(4)应尽量避免走线的弯曲,避免在系统中引入共模噪声,这将影响差分对的信号完整性和EMI。所有走线的弯曲角度应该大于等于135度,差分对走线的间距保持20mil以上,弯曲带来的走线最 短应该大于1.5倍走线的宽度。

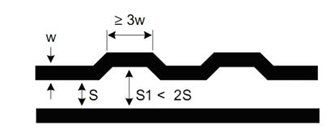

当一段蛇形线用来和另外一段走线来进行长度匹配,如图2所示,每段长弯折的长度必须至少有15mil(3倍于5mil的线宽)。蛇形线弯折部分和差分线的另一条线的最 大距离必须小于正常差分线距的2倍。

图2蛇形走线

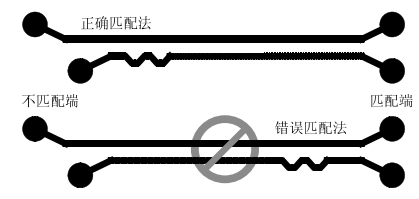

(5)差分对中两条数据线的长度差距需在5mil以内,每一部分都要求长度匹配。在对差分线进行长度匹配时,匹配设计的位置应该靠近长度不匹配所在的位置,如图3所示。但对传输对和接收对的长度匹配没有做具体要求,即只要求差分线内部而不是不同的差分对之间要求长度匹配。在扇出区域可以允许有5mil和10mil的线距。50mil内的走线可以不需要参考平面。长度匹配应靠近信号管脚,并且长度匹配将能通过小角度弯曲设计。

图3PCI-E差分对长度匹配设计

为了最 小化长度的不匹配,左弯曲的数量应该尽可能的和右弯曲的数量相等。当一段蛇形线用来和另外一段走线来进行长度匹配,每段长弯折的长度必须大于三倍线宽。蛇形线弯折部分和差分线的另一条线的最 大距离必须小于正常差分线距的两倍。并且,当采用多重弯曲布线到一个管脚进行长度匹配时非匹配部分的长度应该小于等于45mil。

(6)PCI-E需要在发射端和接收端之间交流耦合,并且耦合电容一般是紧靠发射端。

差分对两个信号的交流耦合电容必须有相同的电容值,相同的封装尺寸,并且位置对称。如果可能的话,传输对差分线应该在顶层走线。电容值必须介于75nF到200nF之间,最 好是100nF。推荐使用0402的贴片封装,0603的封装也是可接受的,但是不允许使用插件封装。差分对的两个信号线的电容器输入输出走线应当对称的。尽量减少追踪分离匹配,差分对走线分离到管脚的的长度也应尽量短。

全新OptoTEC®MSX多级热电制冷器可提供超紧凑设计,实现真空中高达100至120°C温差

全新OptoTEC®MSX多级热电制冷器可提供超紧凑设计,实现真空中高达100至120°C温差 Altera Agilex 3/5 FPGA和SoC的功能特性

Altera Agilex 3/5 FPGA和SoC的功能特性 大模型实战课:用Lattepanda Sigma开发板实现语音控制灯光

大模型实战课:用Lattepanda Sigma开发板实现语音控制灯光

慧聪电子网微信公众号

慧聪电子网微信公众号

慧聪电子网微信视频号

慧聪电子网微信视频号

精彩评论