引言:在需要多个FPGA芯片的应用中,如果JTAG链上所有FPGA采用相同配置,可以通过“成组”加载方式同时加载;如果每个FPGA需要采用不同的配置数据流,可以通过“菊花链”加载方式或者使用外部逻辑依次加载。本文分别介绍串行配置和并行配置模式下的多片FPGA配置数据流加载方式。

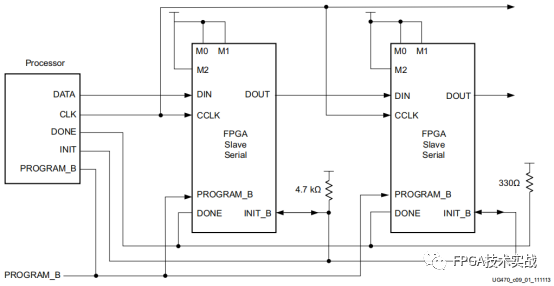

菊花链串行配置模式(串行,多片FPGA采用不同配置流)单一配置源可以通过利用串行菊花链方式加载多片7系列FPGA。在串行菊花链中,器件通过DIN管脚接收配置数据,通过DOU管脚将配置数据传输给下游器件。离配置源最近的器件称为最上游器件,离配置源最远的器件称为最下游器件。如下图所示。

图1 Slave串行模式菊花链配置

在串行菊花链中,所有器件都设置为串行模式,配置时钟由外部提供,如图1中的Processor设备。如图1所示:

1)DONE管脚为开路输出,在Slave串行菊花链中应连接在一起,在最远一片FPGA上拉;

2)INIT_B管脚为双向管脚,开路,需要外部上拉电阻;

3)比特流启动时钟必须设置为CCLK。

串行菊花链中的第一个器件是最后加载数据流的。在配置链中的最后一个器件完成配置,并通过CRC校验,进入启动顺序。在所有器件释放它们的DONE管脚后,DONE信号上拉为高或者有链路中第一个器件驱动为高。

7系列FPGA与早期Virtex/Spartan系列FPGA串行菊花链连接考虑

1)许多较旧的FPGA设备无法接受7系列设备所能产生的CCLK频率。选择链中所有设备支持的配置CCLK速度;

2)7系列设备应始终位于串行菊花链的开头,而较旧的系列设备位于链的末端;

3)为7系列FPGA位流选项提供的指南应尽可能适用于串行菊花链中的所有设备;

4)设备可通过其DOUT引脚的配置位数有限。对于从Virtex II系列开始的7系列和Virtex设备,限制为4294967264位。对于Spartan-6和Spartan-3代设备,限制为2147483632位。所有下游设备的比特流长度总和不得超过此数字。

串行菊花链配置设计要点

1)启动顺序

应在DONE之前或在DONE的同一周期内释放,以确保所有DONE引脚释放后,设备可正常工作。

2)连接所有DONE管脚

所有设备的DONE引脚必须以串行菊花链连接,以防止配置失败。出于调试目的,有一种断开单个DONE的方法通常很有用,从而可以通过串行或JTAG接口单独配置设备。

3)DONE管脚上升时间

释放所有DONE引脚后,DONE引脚应从逻辑0上升到逻辑1。如果DONE信号上升需要额外的时间,可以通过DonePipe选项设置,参看UG628。

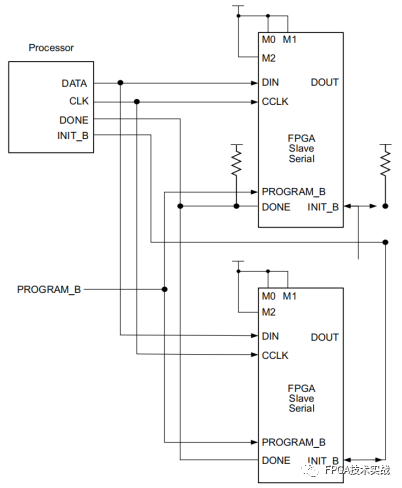

2.成组串行配置模式(串行,多片FPGA采用相同配置流)

使用成组串行配置设置,可以从同一位流源同时配置多个设备(图9-2)。在这种布置中,串行配置引脚被连接在一起,使得每个设备看到相同的信号转变。对于成组串行配置,所有设备必须相同。配置可以由外部配置控制器驱动,从闪存或其他存储器读取位流。

图2 成组串行配置模式 如图2所示:

1)DONE引脚为漏极开路输出;

2)INIT_B引脚是双向开放漏极引脚。需要外部上拉电阻器;

3)必须为串行配置的CCLK设置启动时钟设置;

4)对于成组串行配置,所有设备必须相同(相同的ID CODE),并且必须使用相同的比特流进行配置。

成组串行配置考虑要点

1)启动顺序

应在DONE之前或在DONE的同一周期内释放,以确保所有DONE引脚释放后,设备可正常工作。

2)DONE管脚可断开

出于调试目的,有一种断开单个DONE的方法通常很有用,从而可以通过串行或JTAG接口单独配置设备。

3)CCLK作为电路板时钟信号布局布线

CCLK信号相对较慢,但7系列FPGA输入缓冲器上的边缘速率非常快。即使CCLK信号上的轻微信号完整性问题也会导致配置失败。典型的故障症状是DONE仍然为低,INIT_B为高。因此建议采用注重信号完整性的设计实践,包括IBIS的信号完整性仿真。

4)用于组合串行配置的PROM

用于组合串行配置的PROM文件与用于配置单个设备的PROM相同。没有特殊的PROM文件注意事项。

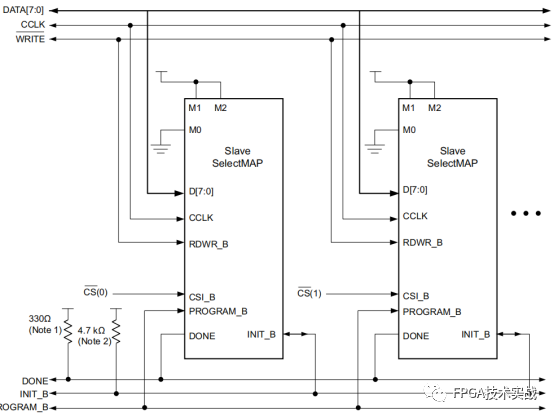

3.成组串行配置模式(并行Slave,多片FPGA采用不同配置流)

处于从属SelectMAP模式的多个7系列设备可以连接在一个公共SelectMAP总线上,如图3所示。在SelectMAP总线中,DATA、CCLK、RDWR_B、PROGRAM_B、DONE和INIT_B引脚在所有设备之间共享公共连接。

为了允许单独访问每个设备,不得将CSI_B(芯片选择)输入连接在一起。需要CSI_B信号的外部控制,通常由微处理器或CPLD提供。

图3 从属SelectMAP模式的多个7系列设备

如果要在配置后对设备执行回读,则必须正确处理RDWR_B信号。否则,RDWR_B可能被绑定为低。

如图3所示:

1)DONE引脚为漏极开路输出;

2)INIT_B引脚是双向开放漏极引脚。需要外部上拉电阻器;

3)不支持回退重新配置;

4)必须为SelectMAP配置的CCLK设置启动时钟设置;

5)需要诸如微处理器或CPLD的外部控制器来控制配置;

6)数据总线可以是x8、x16或x32(用于从属SelectMAP)。

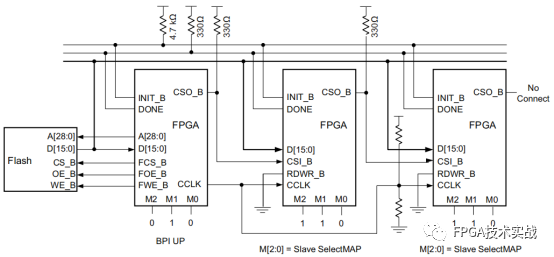

4. 并行菊花链配置模式(主/从并行,多片FPGA采用不同配置流)

7系列FPGA配置支持并行菊花链。图4显示了BPI模式下主导设备的示例示意图。

主导设备也可以处于主或从SelectMAP模式。D[15:00]、CCLK、RDWR_B、PROGRAM_B、DONE和INIT_B引脚在所有设备之间共享公共连接。CSI_B引脚为菊花链。

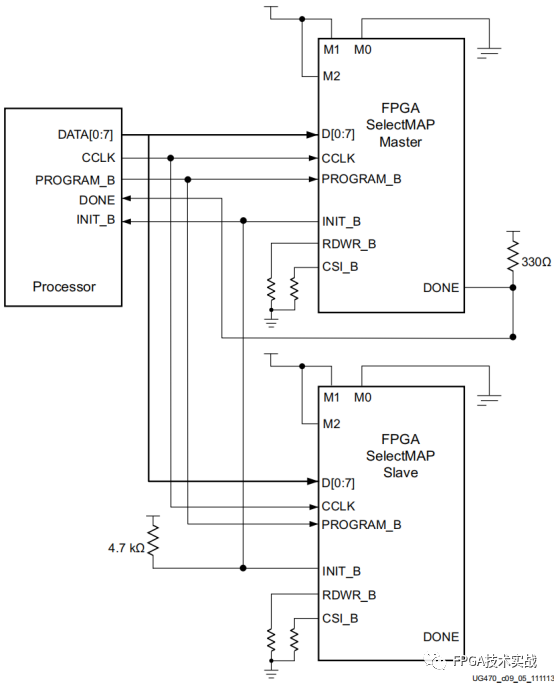

图4 并行菊花链

如图4所示:

1)DONE引脚为漏极开路输出;

2)INIT_B引脚是双向开放漏极引脚,需要外部上拉;

3)必须为SelectMAP配置的CCLK设置启动时钟设置;

4)应启用FCS_B、FWE_B、FOE_B、CSO_B弱上拉电阻器,否则每个引脚需要外部上拉电阻器。默认情况下,所有多功能I/O都具有配置后的弱下拉;

5)链中的第一个设备可以是主SelectMAP、从SelectMAP或BPI。以下设备必须处于从属SelectMAP模式;

6)不支持并行菊花链方案中的回读;

7)不支持回退重新配置。

5. 并行成组配置模式(并行,多片FPGA采用相同配置流)

也可以通过使用成组的SelectMAP配置,使用相同的配置位流同时配置多个设备。

如图5所示,在成组SelectMAP布置中,两个或更多设备的CSI_B引脚连接在一起(或连接到GND),使所有设备识别D引脚上显示的数据。

图5 成组的SelectMAP配置

如图5所示,如果外部振荡器可用,所有设备都可以设置为Slave SelectMAP模式。

1)不支持同步SelectMAP模式;

2)不支持回退重新配置;

3)DONE引脚为漏极开路输出;

4)INIT_B引脚是一个双向开放漏极引脚,需要外部上拉电阻器;

5)必须为SelectMAP配置的CCLK设置启动时钟设置;

6)公共DONE信号上需要一个外部上拉电阻器。由于扇出增加,设计者必须仔细关注信号的完整性。建议进行信号完整性模拟;

7)如果CSI_B信号连接在一起,则无法进行回读,因为所有设备都同时尝试驱动数据信号。

全新OptoTEC®MSX多级热电制冷器可提供超紧凑设计,实现真空中高达100至120°C温差

全新OptoTEC®MSX多级热电制冷器可提供超紧凑设计,实现真空中高达100至120°C温差 Altera Agilex 3/5 FPGA和SoC的功能特性

Altera Agilex 3/5 FPGA和SoC的功能特性 大模型实战课:用Lattepanda Sigma开发板实现语音控制灯光

大模型实战课:用Lattepanda Sigma开发板实现语音控制灯光

慧聪电子网微信公众号

慧聪电子网微信公众号

慧聪电子网微信视频号

慧聪电子网微信视频号

精彩评论