设计的主要流程:

1、规格制定

芯片规格: 芯片需要达到的具体功能和性能方面的要求

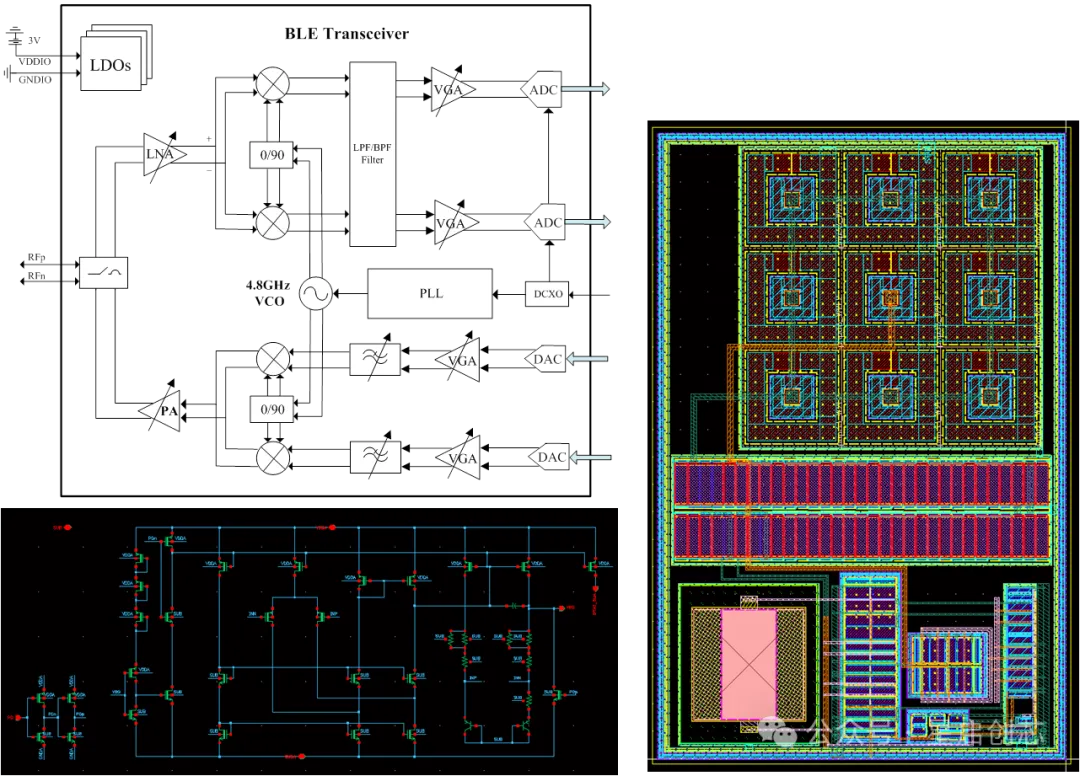

2、详细设计

就是根据规格要求,实施具体架构,划分模块功能。

3、HDL编码

使用硬件描述语言(vhdl Verilog hdl )将功能以代码的形式描述实现。换句话也就是说将实际的硬件电路功能通过HDL语言描述起来,形成RTL代码(使用cadence软件)

4、仿真验证

仿真验证就是检验编码设计的正确性,仿真验证工具Mentor公司的Modelsim,Synopsys的VCS,还有Cadence的NC-Verilog均可以对RTL级的代码进行设计验证?(使用Cadence或Modelsim或Synopsys的VCS等软件)

5、STA

Static Timing Analysis(STA),静态时序分析,属于验证范畴,它主要是在时序上对电路进行验证,检查电路是否存在建立时间(setup time)和保持时间(hold time)的违例(violation)。一个寄存器出现这两个时序违例时,是没有办法正确采样数据和输出数据的,所以以寄存器为基础的数字芯片功能肯定会出现问题。(Synopsys的Prime Time)

6、形式验证

是验证范畴,它是从功能上(STA是时序上)对综合后的网表进行验证。常用的就是等价性检查方法,以功能验证后的HDL设计为参考,对比综合后的网表功能,他们是否在功能上存在等价性。这样做是为了保证在逻辑综合过程中没有改变原先HDL描述的电路功能。(形式验证工具有Synopsys的Formality)

从设计程度上来讲,前端设计的结果就是得到了芯片的门级网表电路

Backend design flow后端设计流程:

1、DFT

Design ForTest,可测性设计。芯片内部往往都自带测试电路,DFT的目的就是在设计的时候就考虑将来的测试。DFT的常见方法就是,在设计中插入扫描链,将非扫描单元(如寄存器)变为扫描单元。关于DFT,有些书上有详细介绍,对照图片就好理解一点。(DFT工具Synopsys的DFT Compiler)

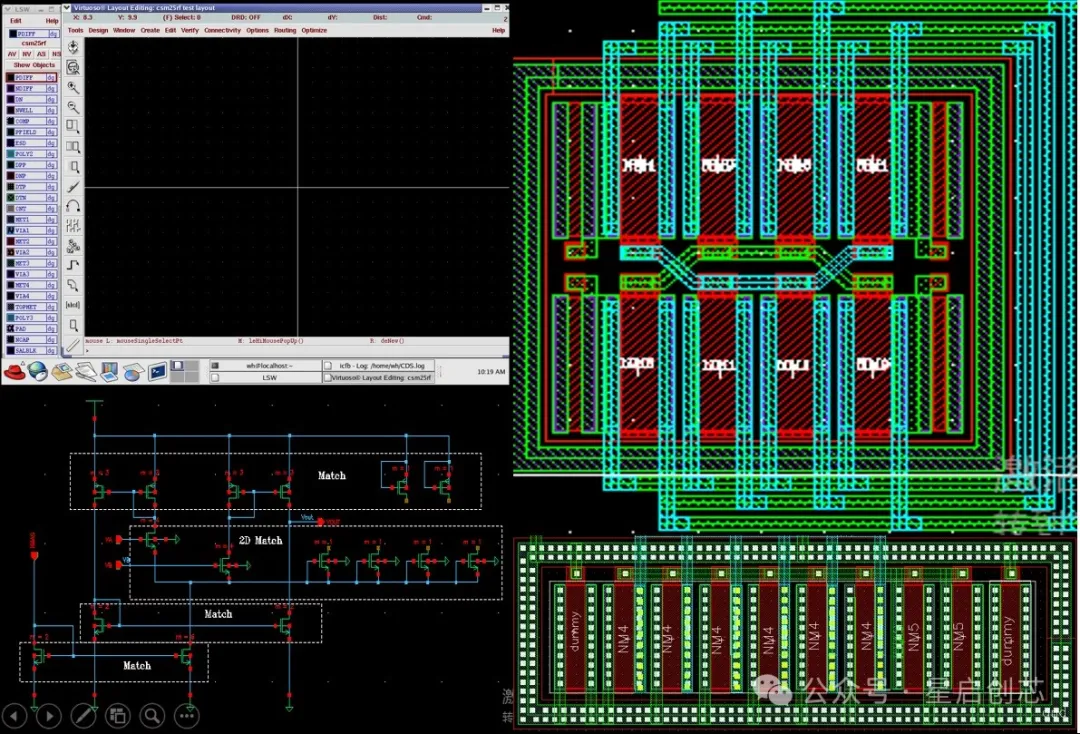

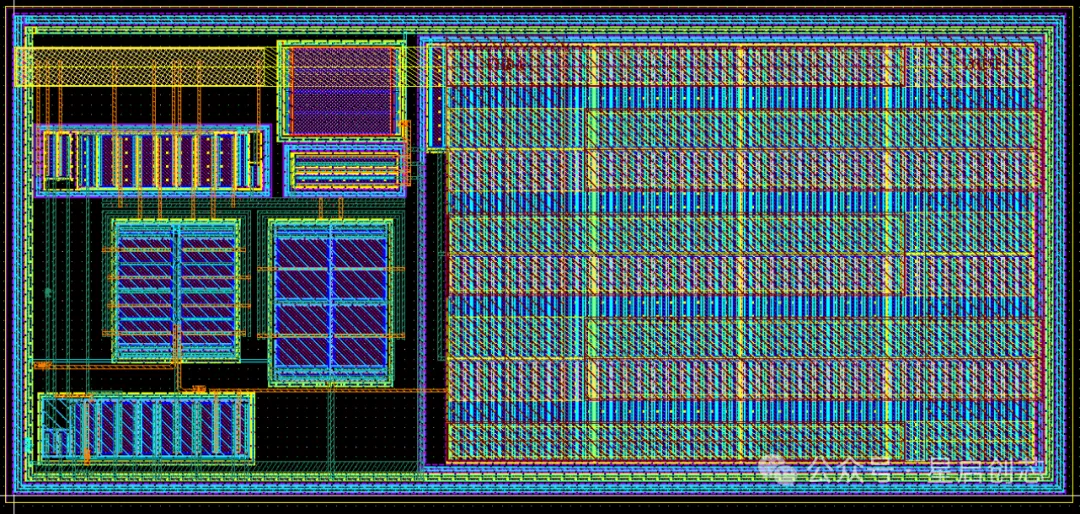

2、布局规划(FloorPlan)

布局规划就是放置芯片的宏单元模块,在总体上确定各种功能电路的摆放位置,如IP模块,RAM,I/O引脚等等。布局规划能直接影响芯片最终的面积。(工具为Synopsys的Astro)

3、CTS

Clock Tree Synthesis,时钟综合,简单点说就是时钟的布线。由于时钟信号在数字芯片的全局指挥作用,它的分布应该是对称式的连到各个寄存器单元,从而使时钟从同一个时钟源到达各个寄存器时,时钟延迟差异最小。这也是为什么时钟信号需要单独布线的原因。CTS工具,(Synopsys的Physical Compiler)

4、布线(Place & Route)

这里的布线是指普通信号布线了,包括各种标准单元(基本逻辑门电路)之间的走线。比如我们平常听到的0.13um工艺,或者说90nm工艺,实际上就是这里金属布线可以达到的最小宽度,从微观上看就是MOS管的沟道长度。(工具Synopsys的Astro)

5、寄生参数提取

由于导线本身存在的电阻,相邻导线之间的互感,耦合电容在芯片内部会产生信号噪声,串扰和反射。这些效应会产生信号完整性问题,导致信号电压波动和变化,如果严重就会导致信号失真错误。提取寄生参数进行再次的分析验证,分析信号完整性问题是非常重要的。(工具Synopsys的Star-RCXT)

6、版图物理验证

对完成布线的物理版图进行功能和时序上的验证,验证项目很多,如LVS(Layout Vs Schematic)验证,简单说,就是版图与逻辑综合后的门级电路图的对比验证;DRC(Design Rule Checking):设计规则检查,检查连线间距,连线宽度等是否满足工艺要求,ERC(Electrical Rule Checking):电气规则检查,检查短路和开路等电气规则违例;等等。工具为Synopsys的Hercules实际的后端流程还包括电路功耗分析,以及随着制造工艺不断进步产生的DFM(可制造性设计)问题。物理版图验证完成也就是整个芯片设计阶段完成。

7、物理版图以GDSII的文件格式交给芯片代工厂(称为Foundry)在晶圆硅片上做出实际的电路,

8、再进行封装和测试。

注释:(1)VCS是编译型Verilog模拟器 简称VCS.

(2)Design Compiler为Synopsys公司逻辑合成工具,简称DC

(3) IC Compiler是Synopsys新一代布局布线系统(Astro是前一代布局布线系统).简称IC.

(4)PrimeTime是针对复杂、百万门芯片进行全芯片、门级静态时序分析的工具。简称PT.

(5)HerculesTM可以进行层次化的物理层验证,以确保版图与芯片的一致性

(6)Star-RCXT是电子设计自动化(EDA)领域内寄生参数提取解决方案的黄金标准

(7)Synopsys 的LEDA是一种可编程代码设计规则检查器,它提供全芯片级混合语言(Verilog和 VHDL)处理能力,从而加快了复杂的SOC设计的开发

(8)Formality是一种等效性检测工具,采用形式验证的技术来判断一个设计的两个版本在功能上是否等效,简称FM.

DRC要验证的对象是版图,我们的版图一般是通过两种方法得到的。一种是用virtuoso等版图编辑工具手工绘制。这在模拟设计中较为普遍。另一种是用Cadence的SE等自动布局布线工具(APR)由网表文件自动产生。

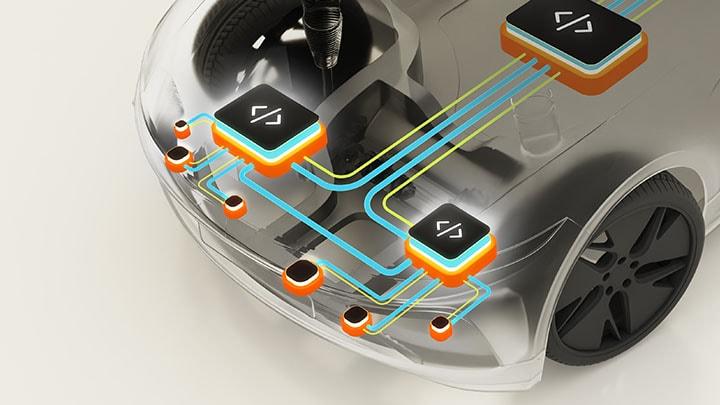

恩智浦发布全新S32K5微控制器系列,推进SDV区域控制架构发展,扩展CoreRide平台

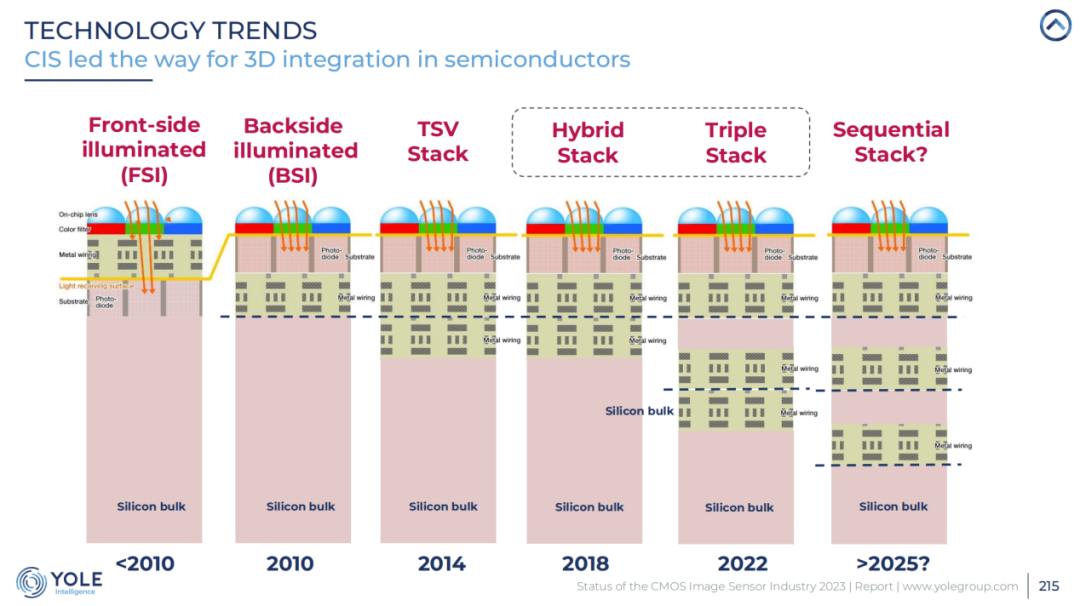

恩智浦发布全新S32K5微控制器系列,推进SDV区域控制架构发展,扩展CoreRide平台 CIS竞争,白热化!

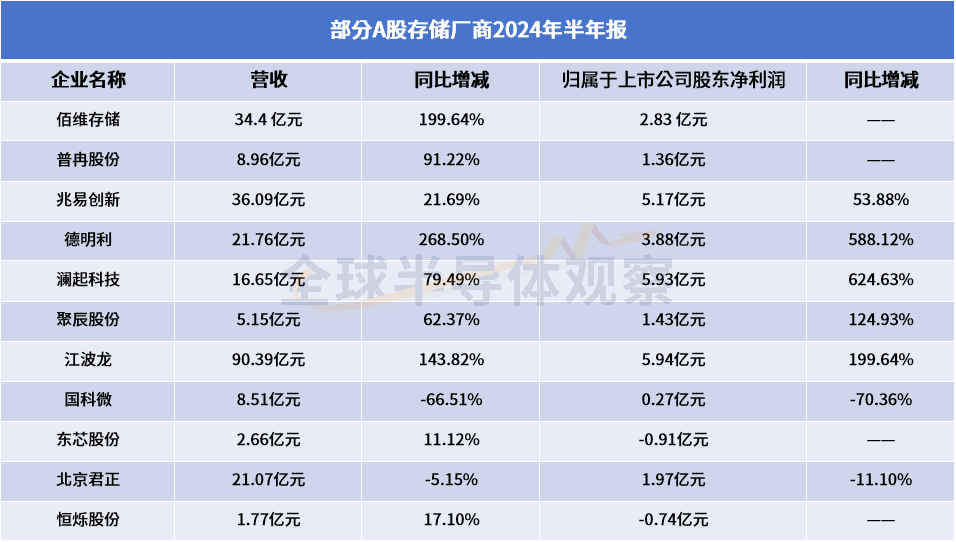

CIS竞争,白热化! 存储产业发展方兴未艾!

存储产业发展方兴未艾! IGBT发明者,获巨额奖金

IGBT发明者,获巨额奖金

慧聪电子网微信公众号

慧聪电子网微信公众号

慧聪电子网微信视频号

慧聪电子网微信视频号

精彩评论