今年ISSCC的议题涵盖毫米波、机器学习、量子等热门关键技术。

摩尔定律逼近极限以及越来越昂贵的先进半导体制程工艺,让整个芯片产业都面临困境。此前,业界通过将多个功能集成到单一芯片中来满足需求,比如手机SoC。但是,SoC集成的复杂度和成本越来越高,让这种方式面临挑战。

在这样的背景下,有一些先进的处理器通过先进的封装和高带宽连接技术,将不同的小芯片(Chiplet)封装成一颗芯片,让芯片性能够持续增加的同时保持成本的可控性,英特尔和AMD就是这种技术的重要推动力。

在ISSCC2020上,英特尔在2月18日的SESSION8中介绍了10nm与22FFL混合封装的Lakefield处理器,采用的是英特尔的Foveros3D封装技术,封装尺寸为12X12X1毫米。Lakefield作为英特尔一款采用了Foveros技术的产品,能够在指甲大小的封装中取得性能、能效的优化平衡。

图1:Foveros3D封装技术,来源英特尔。

Foveros封装技术改变了以往将不同IP模块放置在同一2D平面上的做法,改为3D立体式堆叠。做个类比,传统的方式是将芯片设计为一张煎饼,而新的设计则是将芯片设计成1毫米厚的夹心蛋糕。这样可以提升灵活性,并且不需要整个芯片都采用较先进的工艺,成本也可以更低。

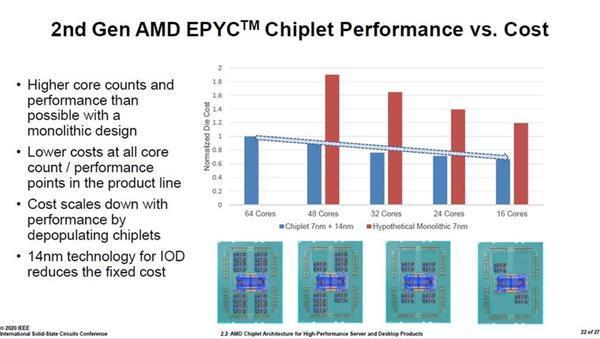

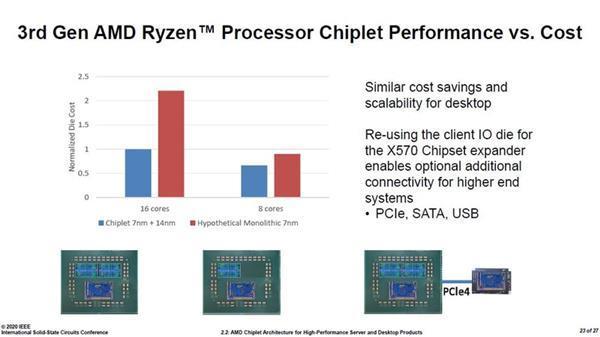

AMD大获成功的Epyc同样使用类似的思路,在此次的ISSCC上,AMD在SESSION2中介绍了使用小芯片架构的高性能服务器产品及性价比的优势。

两者的不同点在于,Epyc使用的是2.5D架构的封装,英特尔使用的是3D堆叠封装。

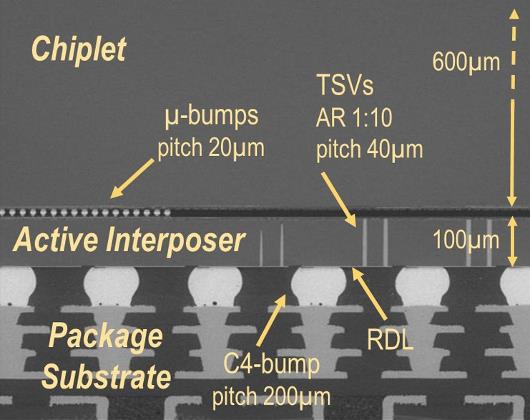

在ISSCC2020会议上,法国公司Leti也发表了一篇论文,介绍了他们使用3D堆栈、有源中介层等技术制造的96核芯片。

根据他们的论文,这个96核芯片有6组CPU单元组成,每组有16个核心,不过Leti没提到CPU内核使用的是ARM还是RISC-V,亦或者是其他,但肯定会是低功耗小核心,使用的也是28nmFD-SOI工艺。

CEA-Leti的科学主管PascalVivet表示,如果要允许不同技术的多个小芯片供应商集成到系统中,有源插入器是小芯片技术的较好选择。

“如果要将接口不兼容的A供应商的小芯片与供应商B的小芯片集成在一起,需要一种将它们‘粘合’在一起的方法。”PascalVivet说,“并且将它们‘粘合’在一起的唯一方法是使用插入器中的有源电路。”

这6组CPU核心使用了3D堆栈技术面对面配置,通过20um微凸点连接到有源中介层上,后者又是通过65nm工艺制造的TSV(硅通孔)技术连接。

在这个96核芯片上,除了CPU及TSV、中介层之外,还集成了调压模块、弹性拓扑总线、3D插件、内存-IO主控及物理层等。

据悉,该系统每平方毫米的传输速率可以达到3TB/s,延迟仅为0.6纳秒。

图:CEA-Leti96核芯片

总之,这款96核芯片集成了大量不同工艺、不同用途的核心,电压管理、IO等外围单元也集成进来了,是异构芯片的一次重要突破。

通过灵活高效、可扩展的缓存一致性架构,这个芯片最终可能扩展到512核,在高性能计算及其他领域有望得到推广应用。

华为昇腾钻石伙伴来了!斯贝达电子CITE2026亮出“深穹+天工+磐岳”全矩阵

华为昇腾钻石伙伴来了!斯贝达电子CITE2026亮出“深穹+天工+磐岳”全矩阵 想开发AI语音项目?用这款套件3分钟搞定!

想开发AI语音项目?用这款套件3分钟搞定! EVIYOS™ HD 25树立紧凑车型安全与通信新标杆

EVIYOS™ HD 25树立紧凑车型安全与通信新标杆 龙虾硬件大赛来了!第十四届中国电子信息博览会(CITE2026)展前揭秘

龙虾硬件大赛来了!第十四届中国电子信息博览会(CITE2026)展前揭秘

慧聪电子网微信公众号

慧聪电子网微信公众号

慧聪电子网微信视频号

慧聪电子网微信视频号

精彩评论