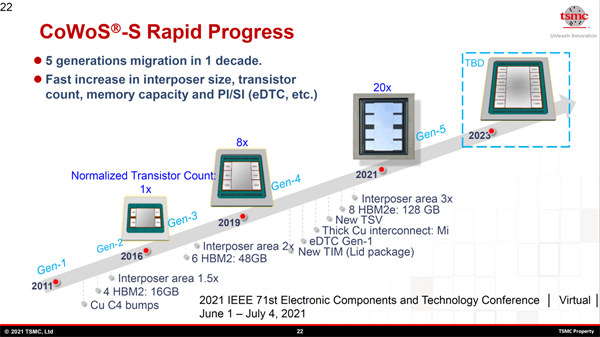

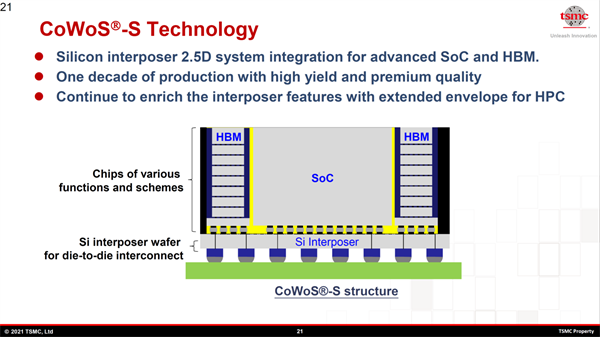

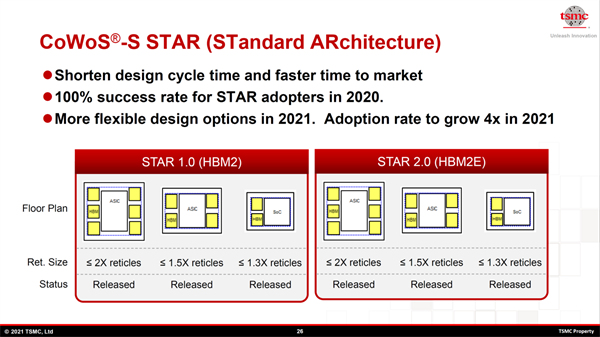

台积电已经制定了其先进的封装技术路线图,并展示了其为下一代小芯片架构和内存解决方案做好准备的下一代 CoWoS 解决方案。台积电在先进的芯片封装技术方面取得了快速进展。在十年内,台积电推出了五代不同的 CoWoS(基板上芯片)封装,且涵盖了消费级与服务器芯片领域。

在 HotChips33 年度会议期间,台积电介绍了该公司最先进的封装技术路线图,并且展示了为下一代小芯片架构和内存设计做好准备的最新一代 CoWoS 解决方案。

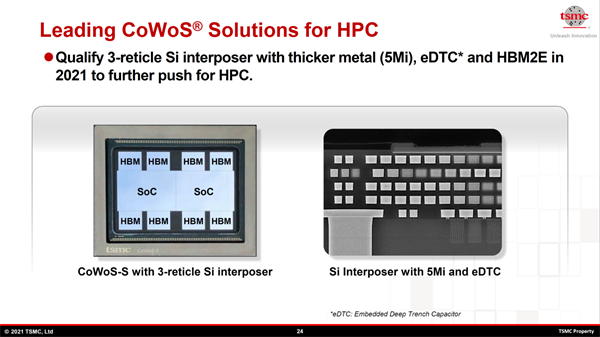

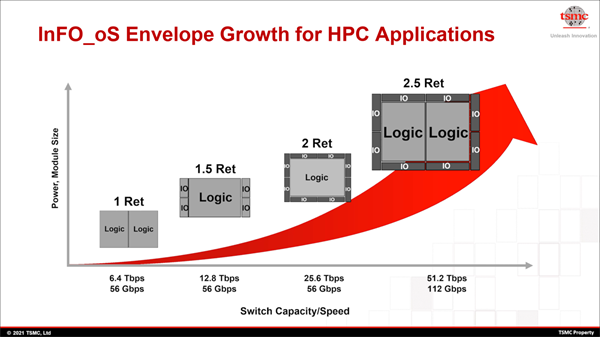

WCCFTech称,预计台积电将在今年晚些时候发布其第 5 代 CoWoS 封装解决方案,其晶体管数量比第 3 代封装解决方案增加 20 倍。新封装将增加 3 倍的中介层面积、8 个 HBM2e 堆栈(容量高达 128 GB)、全新的 硅通孔(TSV)解决方案、厚 CU 互连和新的 TIM(Lid 封装)。

其中最引人注目的解决方案,莫过于使用 TSMC 第 5 代 CoWoS 封装工艺的 AMD MI200“Aldebaran”GPU 。

AMD MI200“Aldebaran”GPU将是第一个在台积电制造和生产的多芯片(MCM)设计 GPU,其采用了 CDNA 2 核心架构,预计可实现一些疯狂的规格参数,例如超过 16,000 个内核、以及高达 128GB 的 HBM2E 内存容量。

NVIDIA 的 Hopper GPU 也将使用 MCM 小芯片架构,预计将在台积电生产。该 GPU 预计将于 2022 年推出,因此我们可以期待 NVIDIA 也能利用 Gen 5 解决方案。

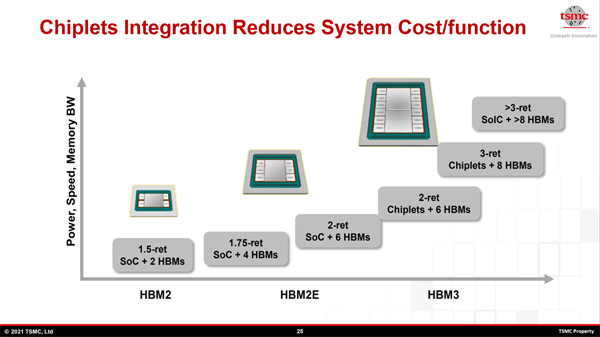

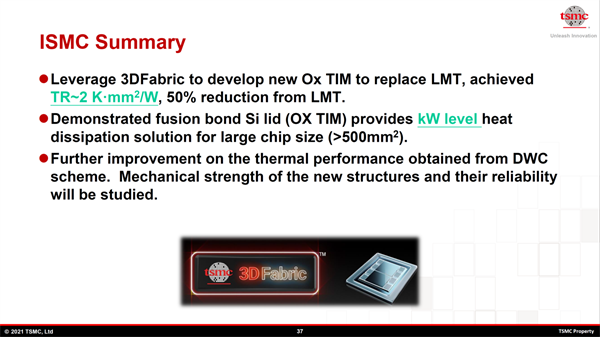

到第 6 代,台积电将拥有更大的掩模版面积,以集成更多的小芯片和更多的 DRAM 封装。封装设计尚未最终确定,台积电预计将在同一封装上容纳多达 8 个 HBM3 DRAM 和两个计算小芯片芯片。台积电还将以 Metal Tim 的形式提供最新的 SOC 散热解决方案,与第一代使用的 Gel TIM 相比,该解决方案有望将封装热阻降低至 0.15 倍。

最后,AMD CNDA 3(MI300)和英伟达 Ampere 的下下一代,都有望采用 TSMC 的 N3 工艺节点进行制造。

参考链接:TSMC Roadmap Lays Out Advanced CoWoS Packaging Technologies, Ready For Next-Gen Chiplet Architectures & HBM3 Memory;Demi Xia编译

Vishay ESD静电保护二极管通过IEEE 10BASE-T1S合规性测试

Vishay ESD静电保护二极管通过IEEE 10BASE-T1S合规性测试 艾迈斯欧司朗发布OSLON™ Black IR:6 C系列:以舱内传感提升驾驶安全,让汽车具备观察与思考的能力

艾迈斯欧司朗发布OSLON™ Black IR:6 C系列:以舱内传感提升驾驶安全,让汽车具备观察与思考的能力 世界级新一代信息技术产业集群建设推进大会在深举办

世界级新一代信息技术产业集群建设推进大会在深举办 华为昇腾钻石伙伴来了!斯贝达电子CITE2026亮出“深穹+天工+磐岳”全矩阵

华为昇腾钻石伙伴来了!斯贝达电子CITE2026亮出“深穹+天工+磐岳”全矩阵

慧聪电子网微信公众号

慧聪电子网微信公众号

慧聪电子网微信视频号

慧聪电子网微信视频号

精彩评论