用于嵌入式设备的系统级芯片(SoC)提供了惊人的集成度。先进的工艺使SoC和MCU开发人员拥有大量的晶体管资源进行操作。这些器件可以集成多核处理器、无线连接、存储器以及图形控制器。然而,即使是最复杂和高度集成的SoC或MCU,也需要一些外部电路来进行电源管理、人机接口或连接到传感器。

因此,在一款设计中,几乎总是散布着比较器、运算放大器、电平转换器、各种逻辑电路和分立晶体管。这些SoC几乎从来不是真正的系统级芯片。在某些情况下,所需的支持逻辑可以用低端FPGA实现。但与用分立器件相比,用FPGA通常成本更高。且因FPGA无法实现模拟或分立组件,因此也不算是一个适当的解决方案。

对于嵌入式设备来说,由于MCU或SoC无法处理所有的传感器、功耗和连接选项,这一挑战将更加明显。任一款嵌入式器件的出货量都远低于用于手机应用的SoC的出货量,这一事实使得情况更加复杂。因此,对典型的MCU或SoC供应商来说,为设计和制造一款支持所有必要的选项组合(permutation)并集成所需的周边支持电路的器件进行大量投入,都是得不偿失的。

那么,设计师是否必须不得已求其次、被迫使用单一逻辑电路、价格虚高的模拟和占大量空间的分立器件进行设计呢?下一代嵌入式设备是否会牺牲宝贵的空间资源、被大量的物料清单(BoM)所累?

所幸答案是否定的,这是因为出现了可配置的混合信号IC(CMIC)。这些器件是可通过一次性可编程(OTP)非易失性存储器配置的模拟和数字电路功能组合。

例如,SilegoTechnology于2009年推出的CMIC。此后,Silego已经完成了1300多个定制设计,并售出了20多亿片可配置器件。

Silego的CMIC提供了各种模拟和数字资源,设计师可以将其配置为混合信号电路。这些资源包括:异步状态机、定时延迟计数器、脉宽调制器、比较器、电压监视器、电压基准、ADC、胶合逻辑和电平转换器。

设计师可以拖放这些资源,并将其设计在原理图捕获工具中“线连”,或可以使用Silego的硬件开发套件来模拟设计。当他们对设计满意时,就可以使用片上OTP内存来编程CMIC器件。CMIC可用于各种必要的混合信号功能,从电机和风扇控制,到传感器接口和电源上电顺控。

节省成本和空间

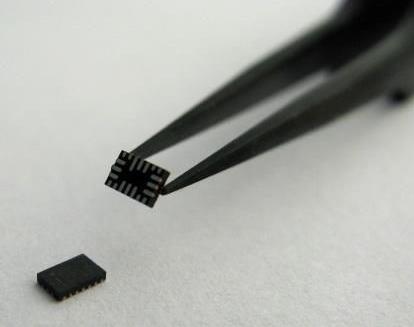

可配置的混合信号IC替代传统的离散和模拟器件,可为嵌入式设计师和制造商提供诸多好处。十几个(或更多)器件占用的宝贵空间,若用于更大容量电池或实现小巧精致的外形,都更物有所值;CMIC可将多个器件集成在一个STQFN微型封装内,封装尺寸从8引脚1.0×1.2mm到20引脚2.0×3.0mm。

传统的电路原型设计需要几天甚至几周的时间来设计PCB、订购器件、制造PCB、焊装、调试和迭代。相比之下,采用CMIC的原型设计要快得多。原理图捕获、仿真和编程可以在同一天完成。更改功能与修改原理图和编程新器件一样简单。

大多数情况下,CMIC的目的在于减少所用离散和模拟器件的BoM成本。根据最近在embedded.com上展示的设计强调,单个0.35美元的CMIC器件取代了1.50美元的分立电平转换和比较器电路。最后,由标准的现成器件搭建的分立电路容易被仿制或山寨。CMIC电路内部与完全定制的IC一样安全,只有设计师或其指定的ODM和供应链合作伙伴可以拿到。

在设计便携式系统时,尺寸和电池续航时间的限制通常是要克服的最严峻挑战。将许多功能集成到小尺寸和严苛功耗预算中的一种传统方式是使用低功耗微控制器,例如TI的MSP430。此类超低功耗微控制器提供高水平的灵活性,并提供小型封装。

SilegoTechnology采取了不同的方法来应对同样问题:在其第五代GreenPAKCMIC产品系列添加用户可编程异步状态机(ASM)宏单元。以下比较说明了当用户考虑是由各种微控制器还是诸如CMIC中的ASM来执行相同作业时,可能的设计权衡和技巧。

处理MCU代码

CMIC的异步状态机包含8个状态和24个可能的决策。ASM代表一个具有多达24个IF..THEN语句的MCU程序。当8个状态ASM功能与硬件输入和输出电路一起考虑时,CMIC可以表示为大致相当于为通用8位和16位MCU编写的大约100行标准C代码。顾名思义,ASM没有时钟并且是事件驱动的,这意味着当没有事件时,ASM保持在一个状态且没有静态功耗。因此,具有有限输入周期的应用可以在泄漏电流功耗水平下工作,室温下,平均消耗电流为几个纳安。

处理嵌入式控制问题

典型的嵌入式控制问题通常涉及通过基于异步外部输入的一组离散状态转换的系统。ASM是这个问题的天生解决者。Silego使ASM满血复活、并进行了现代化处理,缓释了众所周知的危害和竞争条件、编程/配置难题,同时保留了对简单(最多8个状态)、需要少于100行代码的嵌入式控制问题的所有固有的低功耗、低延迟优点。

完胜微控制器与CMICASM的价值

微控制器(MCU)包含处理器、程序代码、堆栈存储器和各种外设。MCU可以容易地执行上述应用示例,但在尺寸和功效方面不理想。将MCU用于连其能力的1%都发挥不到的设计的事例比比皆是。诸如CMIC的ASM等器件非常适合简单的嵌入式控制应用,特别是超低功耗应用。

图1:GreenPackCMIC框图

中断延迟降至纳秒

在MCU上设计状态机通常是由MCU核上运行的软件来完成。在这种情况下,状态被实现为软件指令执行中的点,并且状态转换通过条件软件分支来实现。

MCU还具有处理异步输入的能力,它通过专用的中断控制器硬件和中断服务程序(ISR)来实现。ISR是在硬件中断激活后运行的软件。MCU的一个重要指标是外部中断信号到内核执行相应ISR的第一条指令的时间间隔(所谓的中断延迟)有多短。通常用快速示例量测通用MCU的中断延迟,其值在5到10微秒范围。

ASM的等效中断延迟在纳秒级——等效于历经外部引脚到内部ASM输入之间的几个门的解锁时间。ASM具有从一个状态到下一个状态的延迟。如果CMIC工作在5V电源,则延迟最大为50ns。是的!ASM极快,功耗也极低。

VDD变化

CMICASM工作在较宽的电压范围。由于每个ASM信号路径都由信号长度和门数保证,所以设计正确的ASM可以确保规避了危险和竞争条件。因此,随着VDD变化,传播延迟也随之变化。然而,传播延迟都是匹配的,因此性能得到保证。

另一方面,MCU的钟控信号是与VDD不甚相关的信号。随着VDD变化,MCU的传播延迟发生变化,由于时序不变,因此时序余裕很快被打折。芯片设计对这些设计危害做出了响应,但是将MCU置于稳压器之下,或者通过降低时钟速度会牺牲更多性能。当然,稳压器要耗电,较慢的时钟速度会加大中断延迟。

崩溃与不崩溃

设计和系统缺陷可能导致MCU崩溃。编写不够好的软件、时序问题、中断延迟计算错误、堆栈内存跑飞、内存泄漏(memoryleakages)以及程序存储器中的意外写入都是导致MCU崩溃的常见缺陷。

Silego的ASM采用NVM位硬件配置,没有时序问题;其以纳秒为单位的延迟、无堆栈存储器、无内存泄漏可能、不存在无意写入程序存储器的问题等特点,使其天生对VDD噪声和掉电有很强的免疫力。

基于GUI的工具与典型的MCU工具的对比

使用GreenPAKDesigner开发环境配置CMICASM。该软件看起来像个原理图捕获编辑器,而不是一款编码工具。大多数状态机设计可以在几分钟内实现,将典型的MCU工具几个月的学习曲线缩短到Silego的GPAK几天的学习曲线。

图2:Silego的GreenPackCMIC

总之,具有8状态ASM的小型CMIC可以承载以前一直是MCU专属领域的各种嵌入式控制应用。易于配置的ASM在超快状态转换、泄漏级静态电流功耗、稳健的设计和电源电压容限等方面具有关键优势,它们在IoT、便携式、移动和嵌入式应用中非常重要。此外,CMIC提供了许多好处,从而使嵌入式设计人员的工作更轻松、产品更有利可图。因为电路板空间紧凑,需要尽可能节省空间用于其它有价值的功能(如更大的电池),使得CMIC成为理想的解决方案。此外,它们还大幅减少了传统的模拟和离散器件数,同时也显著降低了有关的风险和压力,从而使采购人员更开心。

观众火热报名中!同期活动亮点纷呈,ES SHOW 2025深圳元器件展10月28-30日邀你共鉴!

观众火热报名中!同期活动亮点纷呈,ES SHOW 2025深圳元器件展10月28-30日邀你共鉴! 品英Pickering为光电信息领域提供先进的开关、仿真方案和测试系统

品英Pickering为光电信息领域提供先进的开关、仿真方案和测试系统 品英Pickering公司仿真方案和测试系统满足航电设备可靠性和安全性等更高要求

品英Pickering公司仿真方案和测试系统满足航电设备可靠性和安全性等更高要求 台积电先进封装订单激增,消息称英伟达独揽七成产能

台积电先进封装订单激增,消息称英伟达独揽七成产能

慧聪电子网微信公众号

慧聪电子网微信公众号

慧聪电子网微信视频号

慧聪电子网微信视频号

精彩评论