工欲善其事,必先利其器。现今的芯片设计已经达到亿门级集成度,即便经验最丰富的设计工程师也无法凭手工完成。

在芯片设计过程中,仿真验证是十分重要的一个环节,以确保芯片进入流片生产环节前符合预期设计性能要求。专门为芯片设计工程师提供仿真和验证工具的EDA细分行业是整个半导体行业生态链中最上游,最高端的节点。

芯片并行仿真技术会是未来EDA设计的主流?

全球EDA市场基本上被三家公司霸占:Cadence、Synopsys和MentorGraphics,其中规模最小的MentorGraphics已经被西门子收购。经过30多年的行业发展和市场竞争,这三家主要的EDA供应商各有自己的独特优势,在全球半导体技术和市场的动态变化中保持相对平衡的格局。

CadenceProtium验证平台大显身手

专注于数字娱乐系统的晶晨半导体(AmLogic)最近推出一款新的多媒体系统级芯片(SoC),其设计周期比传统设计流程缩短2个月。在竞争异常激烈的消费电子市场,比同行提前2个月上市新产品意味着什么,业界人士应该都很清楚。而实现这一芯片设计背后的功臣就是来自Cadence的FPGA原型验证平台ProtiumS1。

新推出的ProtiumS1是Cadence基于FPGA的原型验证平台,晶晨是该验证平台的早期测试参与者之一。受益于该平台独有的设计实现和原型验证加速能力,晶晨可以比以往更早启动SoC设计的软件开发。

据晶晨半导体软件工程总监JerryCao称,使用ProtiumS1平台可以同时执行多个设计实例,大大提高了生产力。此外,该平台与CadencePalladium?Z1企业级硬件仿真加速器共享同一个通用编译流程,可以充分利用现有Cadence验证环境,保持平台间的功能一致性,进一步提高了设计效率。

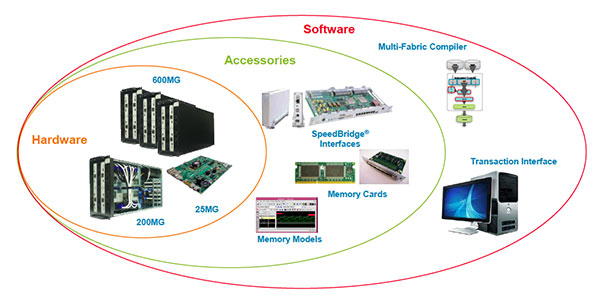

图1:ProtiumS1平台的完整套件

在最近的深圳新产品媒体发布会上,Cadence公司全球副总裁石丰瑜,以及系统与验证事业部产品管理与运营副总裁MichalSiwinski,详细介绍了该公司新推出的这款FPGA原型验证平台。ProtiumS1平台具有如下性能优势:

1、高速原型设计:ProtiumS1平台具备先进的存储单元建模和实现能力,可将原型设计启动时间从数月降至数日,大幅提前固件开发日程。

2、创新的软件调试能力:ProtiumS1平台提供多种提高固件和软件生产力的功能,包括存储单元后门读写、跨分区转存波形、force-release语句,以及运行时钟控制。

3、方便使用与部署:ProtiumS1平台和PalladiumZ1共享一套通用编译流程,现有编译环境的重复利用率最高可达80%,两个平台之间可保持前端流程高度一致。

ProtiumS1采用XilinxVirtexUltraScaleFPGA技术,设计容量比上一代平台提升6倍,性能提高2倍。它与CadencePalladiumZ1企业级仿真平台前端保持一致,使得初始设计启动速度较传统FPGA原型平台提升80%。除晶晨半导体外,ProtiumS1已被网络、消费者类和存储类市场多家厂商先期采用。相信在大规模SoC设计中,它将成为芯片设计工程师的得力助手。

并行仿真已成今年的EDA设计主流

在硬件仿真和FPGA原型验证的推动下,软件环境下的验证已经成为EDA的关键增长领域之一。芯片开发流程越来越需要考虑特定应用的专门需求,现今EDA设计领域的一大主题就是“物联网(IoT)”。物联网跨越多个应用领域,包括与移动设备相连的可穿戴电子产品、与机顶盒相连的智能家居、驾驶员辅助系统(ADAS)和车辆互联等联网汽车应用,以及用于实现自动化的智能工业、医疗保健、城市和能源管理等。

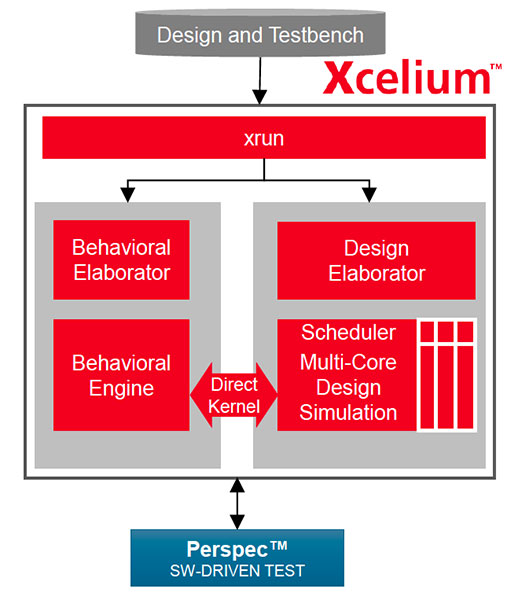

设计验证的四大核心引擎包括仿真、形式验证、硬件加速器和FPGA原型验证,除了继续改善这些核心引擎外,并行仿真也已经成为今年的EDA主流趋势。为满足这一设计需求,Cadence推出了基于多核并行运算技术的并行仿真平台Xcelium。

Xcelium是已经通过产品流片验证的第三代并行仿真平台,其单核版本的性能较Cadence上一代仿真平台平均可提高2倍,多核版本性能平均可提高5倍以上。这一并行仿真平台可以大幅加速系统开发,缩短系统级芯片(SoC)的设计时间,其主要亮点如下:

1、多核仿真:Xcelium源于Cadence收购的Rocketick带来的技术,是基于产品流片的并行仿真平台。利用Xcelium可显着缩短执行时间,在寄存器传输级(RTL)仿真可平均提速3倍,门级仿真可提高5倍,DFT仿真可提高10倍,节约项目时间达数周至数月。

2、应用广泛:Xcelium支持多种设计方式和IEEE标准,工程师无需重新编码即可提升性能。

3、使用方便:Xcelium的编译流程将设计与验证测试环境代码分配至最优引擎,并自动选取最优CPU内核数目,提高执行速度。

4、采用多项专利技术:优化整个SoC验证时间的新技术包括为达到快速验证收敛的SystemVerilogTestbench覆盖率和多核并行编译。

图2:Xcelium的并行仿真架构

Xcelium仿真平台适用于移动、图像、服务器、消费电子、物联网(IoT)和汽车等多个领域,已经在ARM和ST等早期用户中得到了成功应用,并通过了产品流片验证。ARM公司技术服务产品部总经理HobsonBullman表示,Xcelium并行仿真平台对于基于ARM的SoC设计,在门级仿真可获得4倍的性能提升,在RTL仿真可获得5倍的性能提升。基于这些早期试用结果,他相信Xcelium可以帮助ARM及其客户更快和更可靠地交付复杂的SoC。

“针对智能汽车和工业物联网应用中复杂的28nmFD-SOISoC和ASIC设计,快速和可扩展的仿真是满足严苛开发周期的关键!”意法半导体公司CPU团队经理FrancoisOswald说,“我们使用CadenceXcelium并行仿真平台,在串行模式DFT仿真中得到8倍的速度提升,所以数字和混合信号SoC验证团队选择Xcelium作为标准的仿真解决方案。”

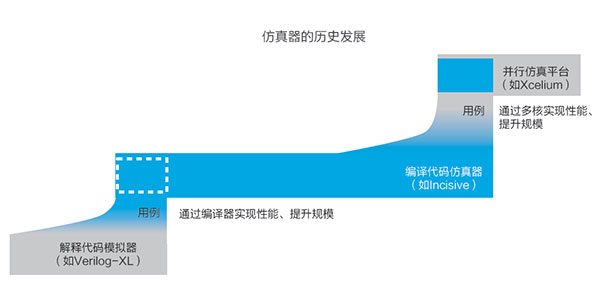

芯片设计仿真技术的发展历史和未来趋势

针对芯片设计的第一代商用仿真技术出现于上世纪80年代后期,以Verilog-XL和RapidSim等解释代码仿真器为代表。其工作机制是先编译成p代码再将其解释执行,因此运行速度极为缓慢,但足够应付当时的小型设计。

随着设计规模慢慢变大,90年代中期出现了编译代码仿真器来满足设计对速度、容量的要求。其工作原理是在运行仿真之前,将源代码转化为机器代码。这是第二代仿真技术,开发比较复杂,用了大概三年时间实现对当时的语言和使用模型仿真的支持。自此第二代仿真器一直是业内主流仿真器,并实现了对e、SystemC、SystemVerilog、CPF和UPF等多种新标准的支持。

然而,随着芯片设计尺寸变得越来越大,越来越复杂,第二代仿真技术已无法满足市场需求。现在的SoC普遍包含百万门级以上的多核设计,测试这些芯片可能耗费数周之久。幸运的是,为了适应SoC尺寸的增长和复杂度的提升,仿真技术也在迅速发展。最近出现的并行仿真正是这样一种通过加快测试速度来提高验证效率的技术。

图3:三代仿真技术的发展

Cadence推出的Xcelium并行仿真平台支持标准多核服务器(多达64核)且采用细粒多进程技术,可以将编译代码仿真平台上运行的仿真分解成可加速和不可加速两个部分。可加速的部分(如门级网标或SystemVerilogRTL部分)由并行引擎处理,验证工程师无需改变测试平台、设计或断言。Xcelium在语言层运作,因此不依赖于工艺节点,也无所谓设计是一个CPU、处理器,还是一个数据通路设计。此外,设计层次也不会造成影响。

图4:第三代并行仿真技术将成为未来20年的主流

前两代仿真技术都各自发展了20年左右。我们有理由相信,全新的并行仿真技术将成为未来20年的仿真基础。

附录

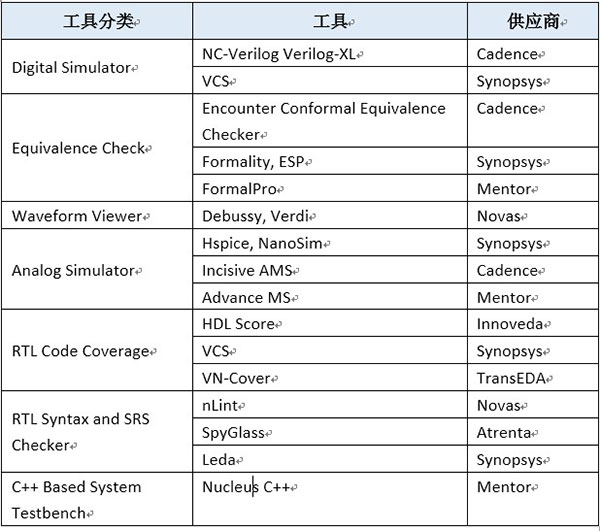

SoC设计中的主要仿真和验证工具

三大EDA供应商都能提供全套的芯片设计解决方案,包括模拟、数字前端、后端、DFT、Signoff等一整套设计工具。Cadence的强项在于模拟和混合信号的模拟仿真和版图设计,但其Signoff的工具偏弱。Synopsys的优势在于数字前端、数字后端和PTsignoff,而Mentor的优势是Calibresignoff和DFT。

此外,Candence和Synopsys还提供IP授权(硬核和软核),这对中小规模的设计公司很具吸引力。授权的IP通常有memory、Serdes和Powermanagement之类的研发成本或门槛相对较高的硬核。

下表列出了一些SOC设计中常用的主要仿真和验证工具,供大家参考。

观众火热报名中!同期活动亮点纷呈,ES SHOW 2025深圳元器件展10月28-30日邀你共鉴!

观众火热报名中!同期活动亮点纷呈,ES SHOW 2025深圳元器件展10月28-30日邀你共鉴! 品英Pickering为光电信息领域提供先进的开关、仿真方案和测试系统

品英Pickering为光电信息领域提供先进的开关、仿真方案和测试系统 品英Pickering公司仿真方案和测试系统满足航电设备可靠性和安全性等更高要求

品英Pickering公司仿真方案和测试系统满足航电设备可靠性和安全性等更高要求 台积电先进封装订单激增,消息称英伟达独揽七成产能

台积电先进封装订单激增,消息称英伟达独揽七成产能

慧聪电子网微信公众号

慧聪电子网微信公众号

慧聪电子网微信视频号

慧聪电子网微信视频号

精彩评论