先进封装是从SoC概念中增加集成度向在封装上配置系统的转变,是与延续摩尔定律的小型化+单片硅不同的做法。

接下来我们就来总结一下目前备受关注的最新封装技术。

嵌入式多芯片互连桥

请看上面幻灯片中的照片。在此横截面中,您可以看到桥接硅片与连接测试块的块之间通过 EMIB 进行互连。硅非常薄。该公司目前正在实现间距为 55 μm 的互连,这大约是有机倒装芯片封装当前基准密度的五倍。使得制造比掩模版(曝光掩模)中使用的硅大三倍以上的芯片成为可能,并且 Sapphire Rapids 被用作数据中心的处理器。

Foveros

技术发展的下一步将是 Foveros。该项目的开发也是从 2017 年开始的。

Foveros 是一种新的互连技术。您可以在上图中看到第一个 Foveros 的横截面。您可以看到顶部tile位于基础tile(芯片或小芯片)上,每个tile都通过硅通孔连接到封装基板,从而允许与封装进行信号通信。这里的tile间互连具有 50μm 节距,与 EMIB 非常相似。这也意味着互连密度比有机倒装芯片高约五倍。第一个使用该技术的产品代号为 Lakefield。这是业界第一个真正的 3D 核心堆栈,位于 Uncore(核心硅除外)之上,占用空间极小。具体来说,Foveros 技术实现了 12x12mm 的占地面积。它还实现了堆叠在封装内部的叠封装存储器。

CO-EMIB:Foveros+EMIB

它被称为 Co-EMIB,下一代封装技术。Co-EMIB 是一项结合了 Foveros 和 EMIB 的技术。这允许更高的包可扩展性。您可以在封装上进行纵向扩展(更大的面积 = 2D 中更宽)和横向扩展(更小的占用空间 = 3D 中堆叠),所有这些都可以通过高密度和高带宽互连来实现。这项技术被用在Intel的GPU Ponte Vecchio上。

然而,Co-EMIB并不是在Lakefield实现商业化的Foveros和在Sapphire Rapids和FPGA实现商业化的EMIB的简单组合。首先,Foveros 已大幅扩展,互连间距从 50μm 增至 36μm。Lakefield)面积约为 100 平方毫米,而Ponte Vecchio则已扩大到超过 600 平方毫米。

另一个演变是Ponte Vecchio的每个底座die都有多个相互堆叠的tile,正如您在上面的金色tile照片中看到的那样。这种多块tile的堆叠也是一种演变。

Lakefield 在一个基础芯片之上有一个计算芯片,而 POP 内存则在其之上。另一方面,Ponte Vecchio 将英特尔和外部代工厂块连接到单个基础芯片上。这已成为该行业有史以来最复杂的情况。事实上,它包含 11 个桥、47 个有源块、5 个处理节点和超过 1000 亿个晶体管。这超过 1000 亿个晶体管数量不包括 HBM。还有三块大面积硅片,尺寸是传统掩模版的三倍多,全部封装在一个封装中。

上面我已经解释了封装技术。传统的多芯片封装长期以来一直用于将 CPU 和 PCH 集成在一个封装上,但从这里开始的演变是向平铺结构发展,以提供更多功能和提高性能。我认为我们明白演变是必要的。这里介绍的新封装技术最近才应用于量产产品,相信它将成为支撑未来封装技术演进的基础。未来,封装技术还需要大量投资。换句话说,在新型半导体的开发中,不仅晶圆晶体管制造技术,封装技术也将成为投资重点。

恩智浦发布全新S32K5微控制器系列,推进SDV区域控制架构发展,扩展CoreRide平台

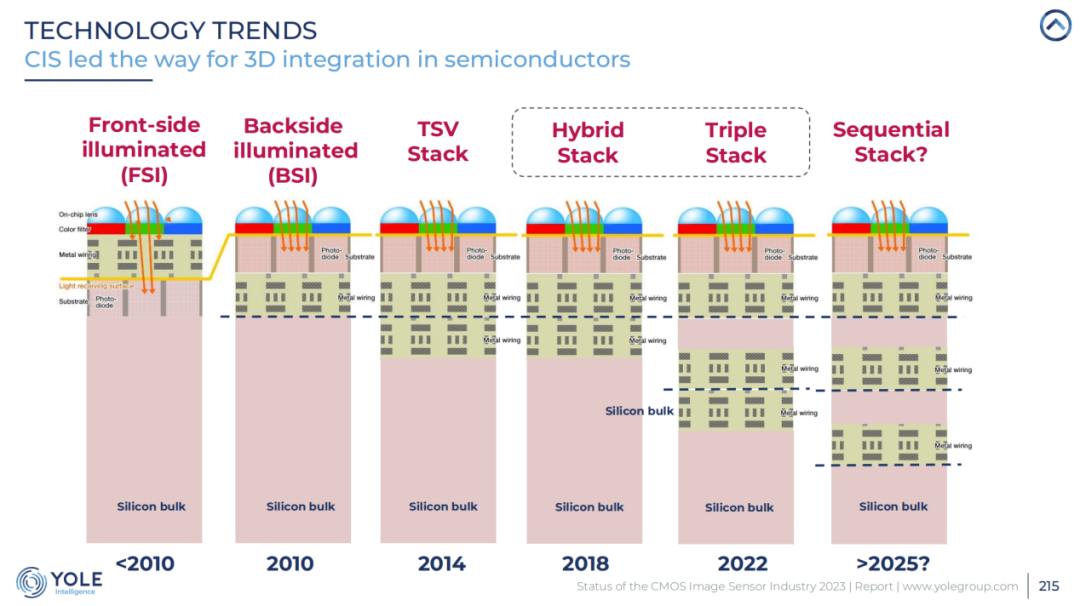

恩智浦发布全新S32K5微控制器系列,推进SDV区域控制架构发展,扩展CoreRide平台 CIS竞争,白热化!

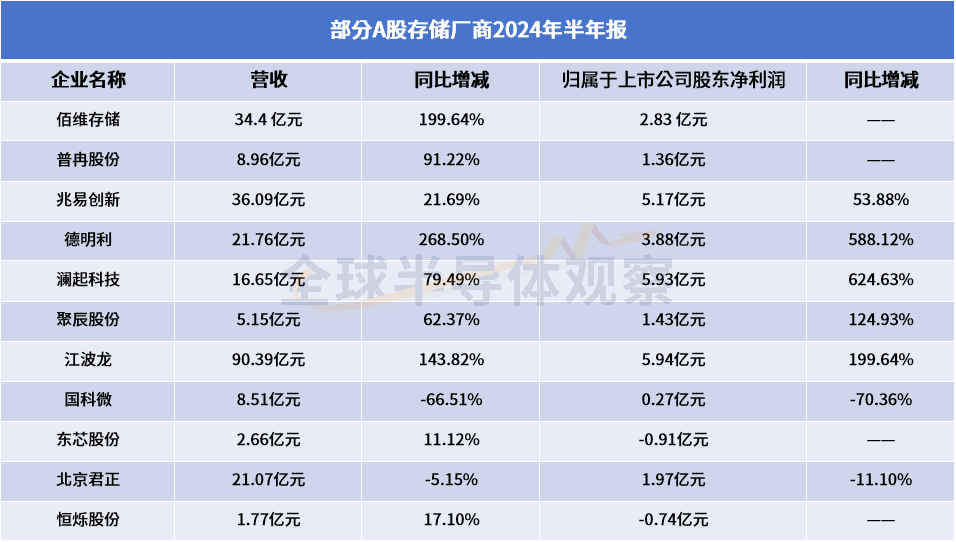

CIS竞争,白热化! 存储产业发展方兴未艾!

存储产业发展方兴未艾! IGBT发明者,获巨额奖金

IGBT发明者,获巨额奖金

慧聪电子网微信公众号

慧聪电子网微信公众号

慧聪电子网微信视频号

慧聪电子网微信视频号

精彩评论