Versal 自适应计算加速平台 (ACAP) 将标量引擎 (Scalar Engine)、自适应引擎 (Adaptable Engine) 和智能引擎(Intelligent Engine) 与领先的存储器和交互技术有机结合,从而为任何应用提供强大的异构加速功能。Versal 架构 PCB 准则已基于前几代进行了精简,以方便 PCB 布局专业人员和硬件设计师使用。

Versal ACAP 中的配电系统

Versal ACAP 包含多条电源轨,每条电源轨都用于一项特定功能,如下表所示。如需了解有关电源名称和电压电平的最新信息,请参阅《Versal AI Core 系列数据手册:DC 和 AC 开关特性》。

适用于存储器接口的 PCB 准则

Versal 架构提供了与以下存储器架构连接的解决方案:

• DDR4

• LPDDR4/4x

• RLDRAM3

• QDR-IV

所有接口的必需存储器布线准则:

1

判定信号走线长度时,请在布线约束中包含封装延迟,除非另行指定。

2

相同字节组中的 DQ 和 DQS 信号应在相同层级内从 Versal 器件布线到 DRAM/DIMM。按适当方式在字节组内包含数据掩码 (DM)。

3

对于多插槽拓扑结构,从一个 DIMM 布线到另一个 DIMM 时,请勿更改层级。

4

信号线必须布线于实体基准内电层上。请勿在空隙处布线。

实体基准内电层上的信号布线

5

请勿在基准内电层分割处布线。

基准内电层分割处的信号布线

6

请将布线置于距离基准内电层和空隙边缘至少 30 mil 外,但引出线区域除外,如下图所示。

引出线区域布线

7

对于双插槽 DIMM 拓扑结构,应将 DIMM #0 布局在离 ACAP 最远的连接器上,以降低 SI 反射的影响。DIMM#1 连接器应布局在离 ACAP 最近的地方。

8

对于使用地址镜像的蛤壳式配置,应确保两条芯片选择线路的终端均充分去耦,并且进出 VTT 的电层/走线厚度足够。

Versal 器件与封装之间的移植

封装移植的高层次目标是确保客户能够在任一管脚兼容封装内跨不同器件使用相同 PCB。封装移植中存在严格的移植设计规则,当前提供的大部分封装都支持在任一给定 Versal 产品组合内进行跨器件移植。但也有跨不同器件系列的封装可提供移植支持。

• VSVA2197 和 VSVD1760:支持在 Versal AI Core 系列与 Prime 系列内进行跨器件移植

• VFVF1760 和 VFVC2197:支持在 Versal Prime 系列与 Premium 系列内进行跨器件移植

智算芯生 · 迭代无界|国微芯五款产品焕新发布,破“芯”局

智算芯生 · 迭代无界|国微芯五款产品焕新发布,破“芯”局 独家对话MIPS CEO:被格芯收购将是一场双赢

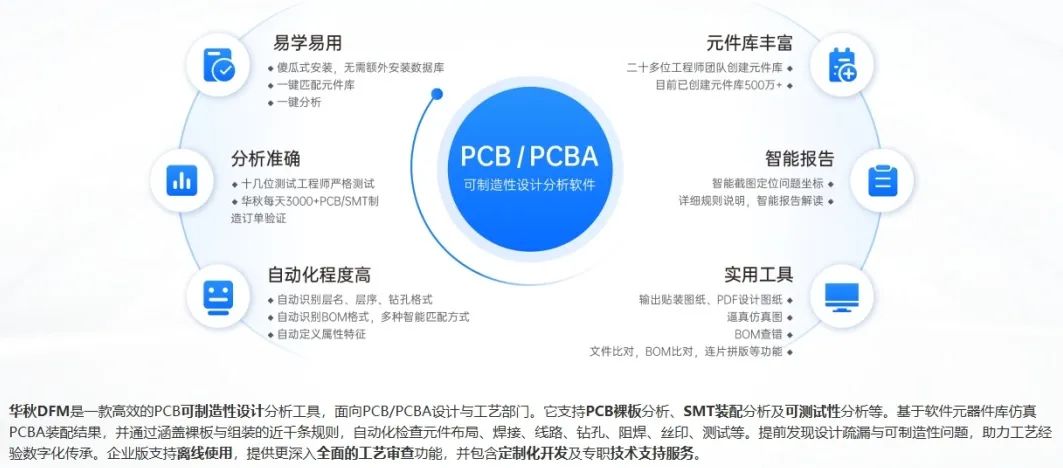

独家对话MIPS CEO:被格芯收购将是一场双赢 【重磅】企业版华秋DFM、华秋CAM正式发布!离线审查+定制开发+专属护航

【重磅】企业版华秋DFM、华秋CAM正式发布!离线审查+定制开发+专属护航 万有引力: 面向机器人/XR 应用的低功耗空间渲染和显示专用芯片EB100

万有引力: 面向机器人/XR 应用的低功耗空间渲染和显示专用芯片EB100

慧聪电子网微信公众号

慧聪电子网微信公众号

慧聪电子网微信视频号

慧聪电子网微信视频号

精彩评论