晶圆代工龙头台积电针对先进封装打造的晶圆级系统整合技术(WLSI)平台,透过导线互连间距密度和系统尺寸上持续升级,发展出创新的晶圆级封装技术系统整合芯片(TSMC-SoIC),除了延续及整合现有整合型扇出(InFO)及基板上晶圆上芯片封装(CoWoS)技术,提供延续摩尔定律机会,并且在系统单芯片(SoC)效能上取得显著的突破。

台积电说明,因为拥有最 先进制程的晶圆或芯片,以及混合匹配的前段3D和后段3D系统整合,客户可以利用台积电独特的从晶圆到封装的整合式服务,来打造具差异化的产品。

台积电打造以3DIC为架构的TSMC-SoIC先进晶圆级封装技术,能将多个小芯片(Chiplet)整合成一个面积更小与轮廓更薄的SoC,透过此项技术,7纳米、5纳米、甚至3纳米的先进SoC能够与多阶层、多功能芯片整合,可实现高速、高频宽、低功耗、高间距密度、最小占用空间的异质3DIC产品。

有别于传统的封装技术,TSMC-SoIC是以关键的铜到铜接合结构,搭配直通矽晶穿孔(TSV)以实现最 先进的3DIC技术。目前台积电已完成TSMC-SoIC制程认证,开发出微米级接合间距(bondingpitch)制程,并获得极高的电性良率与可靠度数据,展现了台积电已准备就绪,具备为任何潜在客户用TSMC-SoIC生产的能力。台积电强调,TSMC-SoIC技术不仅提供延续摩尔定律的机会,并且在SoC效能上取得显著的突破。

台积电持续加强矽中介层(SiInterposer)与CoWoS布局,以因应人工智慧及高效能运算市场快速成长。台积电第四代CoWoS技术已可容纳单个全光罩(full-reticle)尺寸的SoC和多达6个3D高频宽记忆体(HBM)堆叠,第五代CoWoS与博通等客户合作推出2倍光罩尺寸,并将小芯片、SoIC、HBM3等新芯片结构整合。

台积电已完成第五代InFO_PoP(整合型扇出层叠封装)及第二代InFO_oS(整合型扇出暨基板封装)技术并通过认证,支援行动应用和HPC应用。台积电亦开发出新世代整合式被动元件技术(IPD),提供高密度电容器和低有效串联电感(ESL)以增强电性,并已通过InFO_PoP认证。AI与5G行动应用将受惠于强化的InFO_PoP技术,新世代IPD预计于今年开始进入大量生产。

5G封装先出击

5G智能手机同步支援Sub-6GHz及mmWave(毫米波)等多频段,数据机基频芯片或系统单芯片(SoC)的设计及功能更为複杂,晶圆代工龙头台积电除了提供7纳米及5纳米等先进製程晶圆代工,也进一步完成5G手机芯片先进封装供应链布局。其中,台积电针对数据机基频芯片推出可整合记忆体的多芯片堆叠(MUlti-STacking,MUST)封装技术,整合型扇出天线封装(InFO_AiP)下半年将获华为海思採用。

由于5G同步支援多频段、高速资料传输速率、大容量资料上下载等特性,加上5G终端装置亦加入了边缘运算功能,所以5G智能手机搭载的应用处理器、数据机或SoC等5G手机芯片,都需要导入7纳米或5纳米等先进製程,才能在提升运算效能的同时也能有效降低芯片功耗。因此,包括苹果、高通、联发科、华为海思等都已採用台积电7纳米或5纳米量产。

但在5G芯片运算效能大跃进的同时,核心逻辑芯片需要更大容量及更高频宽的记忆体支援,射频前端模组(RFFEM)也需要搭载更多功率放大器(PA)或低噪放大器(LNA)元件,可以解决芯片整合问题的先进封装技术因此成为市场显学。

包括苹果、华为、三星等一线大厂今年所打造的5G智能手机,均大量导入系统级封装(SiP)设计来降低功耗及达到轻薄短小目标,台积电因此推出5G智能手机内建芯片的先进封装技术,以期在争取晶圆代工订单之际,也能透过搭载先进封装製程而提高客户订单的黏著度。

针对5G手机中的应用处理器,台积电已推出InFO_PoP製程并将处理器及MobileDRAM封装成单一芯片。而5G数据机基频芯片因为资料传输量大增,台积电开发出採用InFO製程的多芯片堆叠MUST封装技术,同样能将基频芯片及记忆体整合封装成单一芯片,而台积电也由此开发出3DMiM(MUSTinMUST)的多芯片堆叠封装技术,除了能应用在超高资料量传输的基频芯片,亦能应用在高效能运算(HPC)相关芯片封装,将单颗SoC与16颗记忆体整合堆叠在同一芯片。

再者,台积电InFO製程可提供射频元件或射频收发器的晶圆级封装,但在mmWave所採用的RFFEM模组封装技术上,台积电推出基于InFO製程的InFO_AiP天线封装技术,相较于覆晶AiP封装可明显缩小芯片尺寸及减少厚度。苹果iPhone12搭载天线虽然没有採用台积电InFO_AiP製程,但华为海思有机会在下半年出首 款採用台积电InFO_AiP技术的天线模组并搭载在新一代5G旗舰手机中。

【联创杰检测中心质量分析报告】-5月刊:XILINX常见封装结构

【联创杰检测中心质量分析报告】-5月刊:XILINX常见封装结构 科创板并购简易程序“首单”!中微公司战略收购杭州众硅项目注册生效

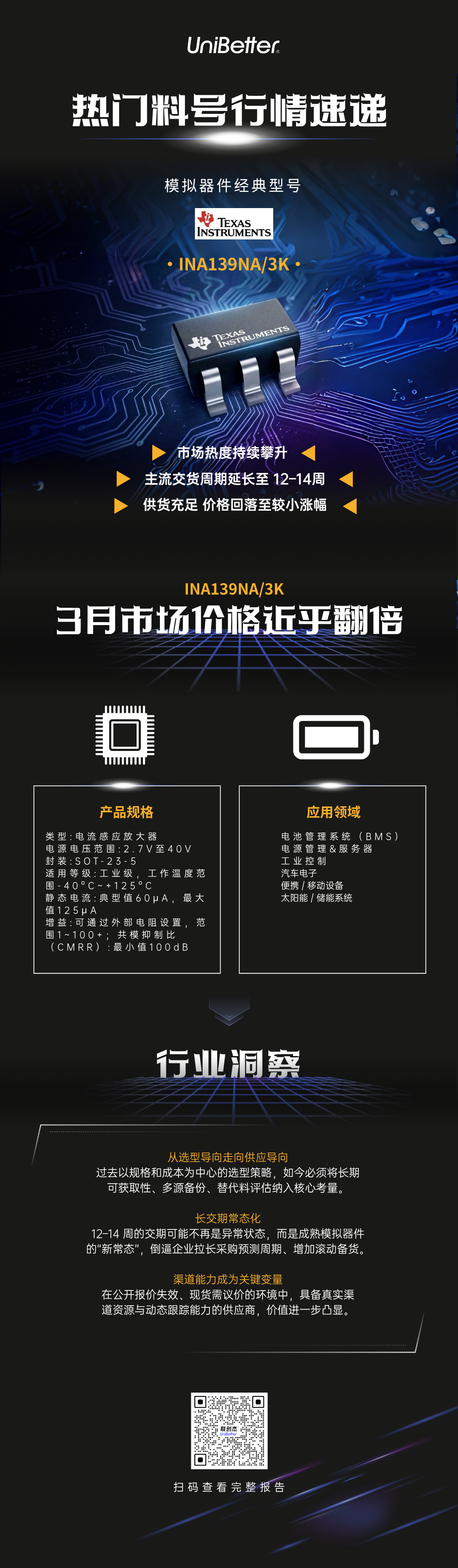

科创板并购简易程序“首单”!中微公司战略收购杭州众硅项目注册生效 热门料号行情速递:INA139NA/3K — 需求猛增,供应链是输赢关键

热门料号行情速递:INA139NA/3K — 需求猛增,供应链是输赢关键 四月存储行情分化!别再闭眼囤货了—联创杰芯片现货市场行情分析2026年4月刊

四月存储行情分化!别再闭眼囤货了—联创杰芯片现货市场行情分析2026年4月刊

慧聪电子网微信公众号

慧聪电子网微信公众号

慧聪电子网微信视频号

慧聪电子网微信视频号

精彩评论