近期,台积电生态系统和联盟管理负责人Dan Kochpatcharin公开表示,台积电将与三星联手研发下一代HBM产品HBM4。这也是三星与台积电首次公开在HBM领域的合作。而HBM领域的另一位巨头SK海力士同样在此前发布公告称,将与台积电合作开发HBM4,预计在2026年投产。两大HBM供应商接连送上橄榄枝,台积电掌握了哪些“关键法宝”?

迭代越来越快 技术越来越难

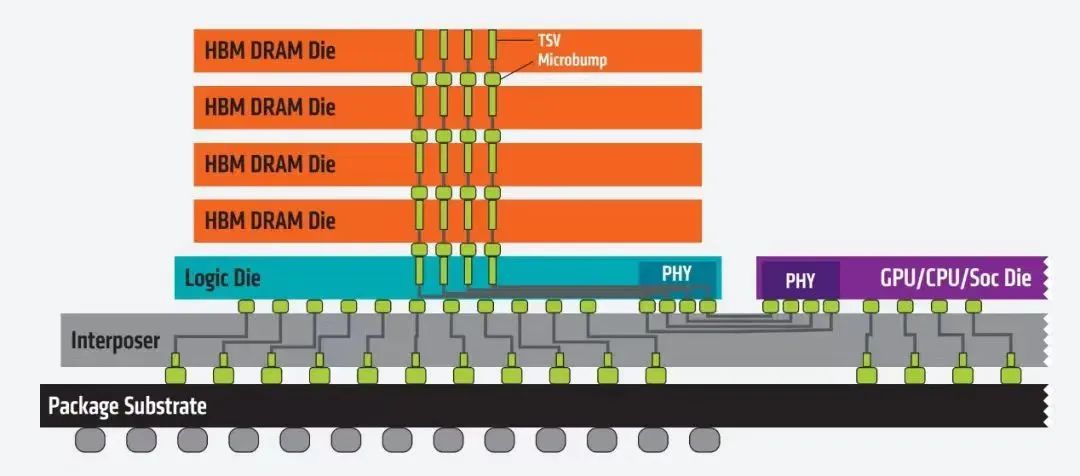

HBM即高带宽存储,由多层DRAM Die垂直堆叠,每层Die通过硅通孔(TSV)技术实现与逻辑Die连接,使得8层、12层Die封装于小体积空间中,从而实现小

HBM的架构示意图(图源:AMD东方证券研究所)

当前,随着AI市场持续增长,AI服务器对于HBM的内存容量和传输带宽提出了更高要求,推动了HBM技术的迭代升级。每一次技术的突破,都会让HBM在带宽、容量、能效、架构以及市场应用等方面取得显著提升,但所需的制造工艺也越来越复杂。

HBM初代产品于2014年由AMD与SK海力士共同推出。作为GDDR产品的竞品,HBM采用了硅通孔(TSV)技术,实现4层die堆叠,可以提供128GB/s带宽和1GB内存,其当时的带宽就已经高于DDR4和GDDR5产品,同时以较小的外形尺寸消耗较低的功率,能更好地满足GPU等带宽需求较高的处理器。性能、尺寸和功耗上的种种优势,让HBM在业内崭露头角。

第二代的HBM于2016年由后来者三星“越级”抢先发布。作为旗下首款HBM产品,三星将每个HBM堆栈容量提升至8GB,使用硅通孔和微凸块(microbump)技术,可以提供256GB/s的带宽,是GDDR5产品带宽的七倍之多。SK海力士则是在2018年正式推出堆叠高度为4层和8层的HBM2,并且引入了伪通道模式,将一个通道分为两个独立的64位I/O子通道,从而降低延迟,提高带宽。

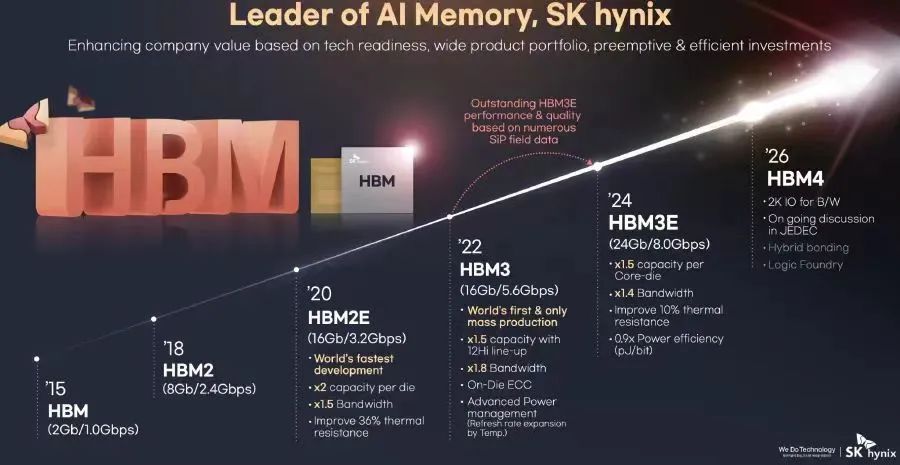

HBM2的加强版HBM2E于2019年再次由三星抢先发布。据了解,这款HBM2E单颗最大容量为16GB,最高可提供3.2Gbps的数据传输速度。而SK海力士则于2020年率先批量生产HBM2E产品,性能比三星的产品更强,在容量同样达到16GB的同时,带宽达到了460GB/s。此外,SK海力士还首次采用了批量回流底部模制填充(MR-MUF)技术,提升了散热性能,使得这款产品的散热性能比上一代的HBM2高出36%。

SK海力士的HBM3E产品(图源:SK海力士官网)

随后的HBM3和其强化版HBM3E都由SK海力士占据主导权,SK海力士的HBM3产品于2022年正式推出,其堆叠层数及管理通道数均有增加,可以提供6.4Gbps传输速度,带宽可达819GB/s,容量提升到24GB。而SK海力士最新的HBM3E产品将使用其1b纳米制造技术(10纳米级的DRAM节点)来生产,并将MR-MUF技术升级为先进MR-MUF4技术,数据传输速度有望提高到8.0GT/s,带宽提高到1TB/s,SK海力士计划今年实施量产HBM3E产品。

制程和封装是两大“拦路虎”

随着每一代产品在性能上的飞跃式提升,HBM对制程和封装技术的要求也更加严苛。

TrendForce集邦咨询分析师许家源表示:“HBM1至HBM2e的堆栈层数仅为4层和8层,制程难度相对较低。但到了HBM3,堆栈层数增加至12层,制程难度大幅提升,HBM4更是要将堆栈层数增加至16层,复杂程度和制造难度都将进一步提升。”

据了解,更先进的制程节点有助于提高HBM的能效比和性能。因此,从HBM1到HBM3E,所采用的制程节点从28纳米进化到10纳米。三星和SK海力士近期发布的信息显示,HBM4将采用5纳米甚至更小的工艺节点,进入先进制程范畴。

SK海力士公布的HBM技术路线图(来源:SK海力士)

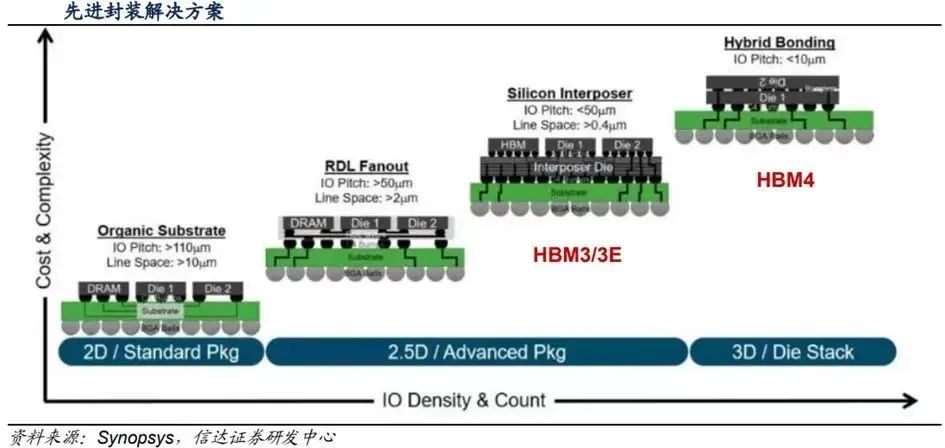

先进封装技术也是同理。除了更先进的TSV技术,HBM还需要MR-MUF技术、混合键合等新一代封装技术加持。

HBM4对先进制程和先进封装技术的需求,让如何保持高良率成为一个难题。在制造过程中,任何一层die出现问题,都可能导致整个堆叠失效。这一系列的难题让三星这个全球排名第二的代工厂商都感到棘手,联合先进制程的霸主台积电似乎成了唯一选择。

台积电掌握核心技术

台积电作为全球领先的半导体制造企业,可以说是当下先进的制程的天花板,并且良率较为稳定,可靠性和安全性在业内首屈一指,这都是研发HBM4的必备条件。

据了解,台积电计划在HBM4生产中采用N12FFC+和N5两种制程技术。N5是一种领先的5纳米制程技术,能够提供更小的晶体管尺寸,实现更高的性能和更低的能耗。这种先进的制程技术能够优化HBM4的逻辑芯片,提升整体的计算效率和能效比。

在封装技术方面,半导体行业专家告诉记者,台积电拥有诸如InFO和CoWoS等先进封装解决方案,能够在芯片之间构建更快速的数据交换路径,有助于解决热管理和信号完整性问题。通过先进的封装技术,台积电能够为HBM4提供更大的带宽和更低的延迟。

这些优势正是SK海力士所渴望的。SK海力士缺乏先进制程的制造能力,和三星又是HBM领域的直接竞争对手,再加上三星的先进制程良率一直是个大问题,双方合作的可能性很低。因此,SK海力士最好的选择就是尽快与台积电达成合作。

于是,在今年4月,SK海力士宣布与台积电签署了一份谅解备忘录,双方将合作生产下一代HBM,并通过先进的封装技术提高逻辑和HBM的集成度。

据了解,两家公司将首先对HBM封装内最底层的基础裸片进行性能改善。SK海力士以往的HBM产品都是基于公司自身制程制造基础裸片,但从HBM4产品开始计划采用台积电的先进逻辑工艺。若在基础裸片采用超细微工艺,可以增加更多的功能。SK海力士计划在2025年下半年推出12层DRAM堆叠的首批HBM4产品,于2026年推出16层堆叠的HBM4E产品,内存带宽将是HBM4的1.4倍。产品面市时间将与英伟达AI加速器发布周期保持一致。SK海力士封装开发副总裁李康旭在“2024异构集成全球峰会”上详细阐述了这一合作的重要性。他指出,通过将逻辑工艺应用于HBM4的基片,可以显著改善性能和能效。

近期,英伟达、台积电和SK海力士又宣布组建“三角联盟”,面向AI需求共同推进HBM4等下一代技术。可以看出,SK海力士想与台积电进行深度绑定。据了解,SK海力士和台积电决定在原计划的12纳米制程基础上,增加5纳米制程来生产HBM4。

在封装技术方面,SK海力士表示,SK海力士独有的先进MR-MUF技术以及混合键合等新一代封装技术,将与台积电独有的CoWoS技术相融合,这对于下一代HBM的发展至关重要。

而三星最初的想法是继续押注自家的4纳米制程。三星一位高管表示:“我们与台积电和SK海力士不同,我们的芯片设计人员直接参与HBM4生产,这是我们的独特优势。”目前,三星已在其设备解决方案部门新设“HBM开发组”,专注于推进HBM4技术。

此外,三星先进封装团队高管Dae Woo Kim在2024年度韩国微电子与封装学会年会上表示,三星成功制造了基于混合键合技术的16层堆叠HBM3内存,该内存样品工作正常,未来16层堆叠混合键合技术将用于HBM4内存量产。

相较现有键合工艺,混合键合无需在DRAM内存层间添加凸块,而是将上下两层直接铜对铜连接,可显著提高信号传输速率,更适合AI计算对高带宽的需求,还可降低DRAM层间距,减少HBM模块整体高度。

但三星近期宣布将与台积电合作研发HBM4,这一“打脸”举动,也侧面反映出三星自身的先进制程和封装技术尚不足以支撑其HBM4研发。

专家告诉记者,三星与台积电将共同开发一种特殊版本的无缓冲HBM4,技术路线与SK海力士的HBM4并不相同,这款产品取消了用于分配电压和防止电气问题的缓冲器,预计能提高40%的功率效率,并减少10%的延迟。三星计划在年底前完成HBM4的流片,为2025年底的大规模生产奠定基础。

三星或将投资入股英特尔

三星或将投资入股英特尔 芯片“大突围”:特朗普100%关税下,谁能靠“美国制造”上岸?

芯片“大突围”:特朗普100%关税下,谁能靠“美国制造”上岸? 龙图光罩90nm掩模版量产,已启动28nm制程掩模版的规划

龙图光罩90nm掩模版量产,已启动28nm制程掩模版的规划

慧聪电子网微信公众号

慧聪电子网微信公众号

慧聪电子网微信视频号

慧聪电子网微信视频号

精彩评论